Altera Nios Development Board Cyclone II Edition User Manual

Page 14

2–2

Reference Manual

Altera Corporation

Nios Development Board Cyclone II Edition

May 2007

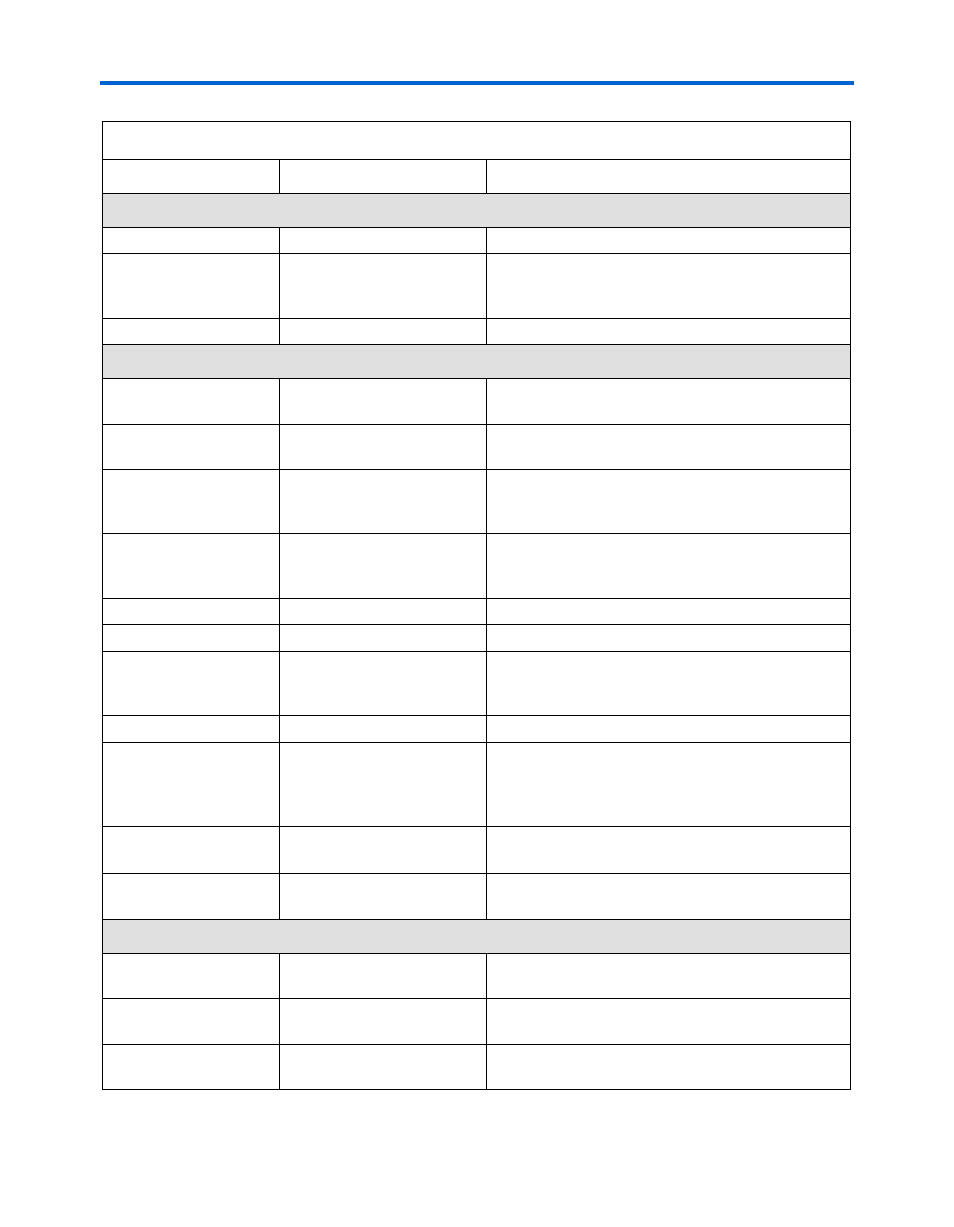

Board Components

Memory

U74

SSRAM memory

2 Mbytes of synchronous SRAM.

U5, LED7

Flash memory

16 Mbytes of nonvolatile memory for use by both the

FPGA and the configuration controller. LED7 lights

whenever the flash chip-enable is asserted.

U63

DDR SDRAM memory

32 Mbytes of DDR SDRAM.

Connections & Interfaces

U4, RJ1

Ethernet MAC/PHY

10/100 Ethernet MAC/PHY chip connected to an RJ-

45 Ethernet connector.

J19

Serial connector

RS-232 serial connector with 5 V-tolerant buffers.

Supports all RS-232 signals.

PROTO1 (J11, J12, J13) Expansion prototype

connector

Expansion headers connecting to 41 I/O pins on the

FPGA. Supplies 3.3V and 5.0V for use by a daughter

card.

PROTO2 (J15, J16, J17) Expansion prototype

connector

Expansion headers connecting to 41 I/O pins on the

FPGA. Supplies 3.3V and 5.0V for use by a daughter

card.

CON3

CompactFlash connector

CompactFlash connector for memory expansion.

JH1, JH2

PMC connector

Expansion connector for a PCI mezzanine card.

J25

Mictor connector

Mictor connector providing access to 27 I/O pins on

the FPGA. Allows debugging Nios II systems using a

First Silicon Solutions (FS2) debug probe.

TP1 – TP8

Test Points

Test points providing access to eight FPGA I/O pins.

J24

JTAG connector

JTAG connection to the FPGA allowing hardware

configuration using the

Quartus

®

II software and software debug using the

Nios II IDE.

J5

JTAG connector

JTAG connection to the MAX

®

configuration

controller.

J27

EPCS configuration header

Connects to the EPCS serial configuration device for

in-system programming.

Configuration & Reset

U3

MAX Configuration controller Altera MAX EPM7256AE device used to configure

the FPGA from flash memory.

U69

Serial configuration device

Altera EPCS64 low-cost serial configuration device to

configure the FPGA.

SW8

CPU Reset button

Push-button switch to reboot the Nios II processor

configured in the FPGA.

Table 2–1. Nios Development Board, Cyclone II Edition Components & Interfaces (Continued)

Board Designation

Name

Description