Epcs64 serial configuration device (u69), Epcs64 serial configuration device (u69) –32 – Altera Nios Development Board Cyclone II Edition User Manual

Page 44

2–32

Reference Manual

Altera Corporation

Nios Development Board Cyclone II Edition

May 2007

Board Components

lists the connections between the FPGA, U3, and the test

points.

EPCS64 Serial

Configuration

Device (U69)

U69 is a serial configuration device connected to the FPGA. Serial

configuration devices are flash memory devices with a serial interface

which can store configuration data, and load the data into the FPGA upon

power up or reconfiguration. U69 can store FPGA configuration data, or

Nios II program data, or both.

lists the connections between U69 and the FPGA.

The SOPC Builder EPCS Serial Flash Controller component enables

Nios II processor systems to access the EPCS device. Nios II processor

systems can read program code or data from the device, and can write

new data into the EPCS device.

U69 is blank by default. The Quartus II software can program FPGA

configuration data (a .pof file) into U69 through an Altera download

cable connected to J27. Alternately, software running on a Nios II

processor design can write configuration data to U69.

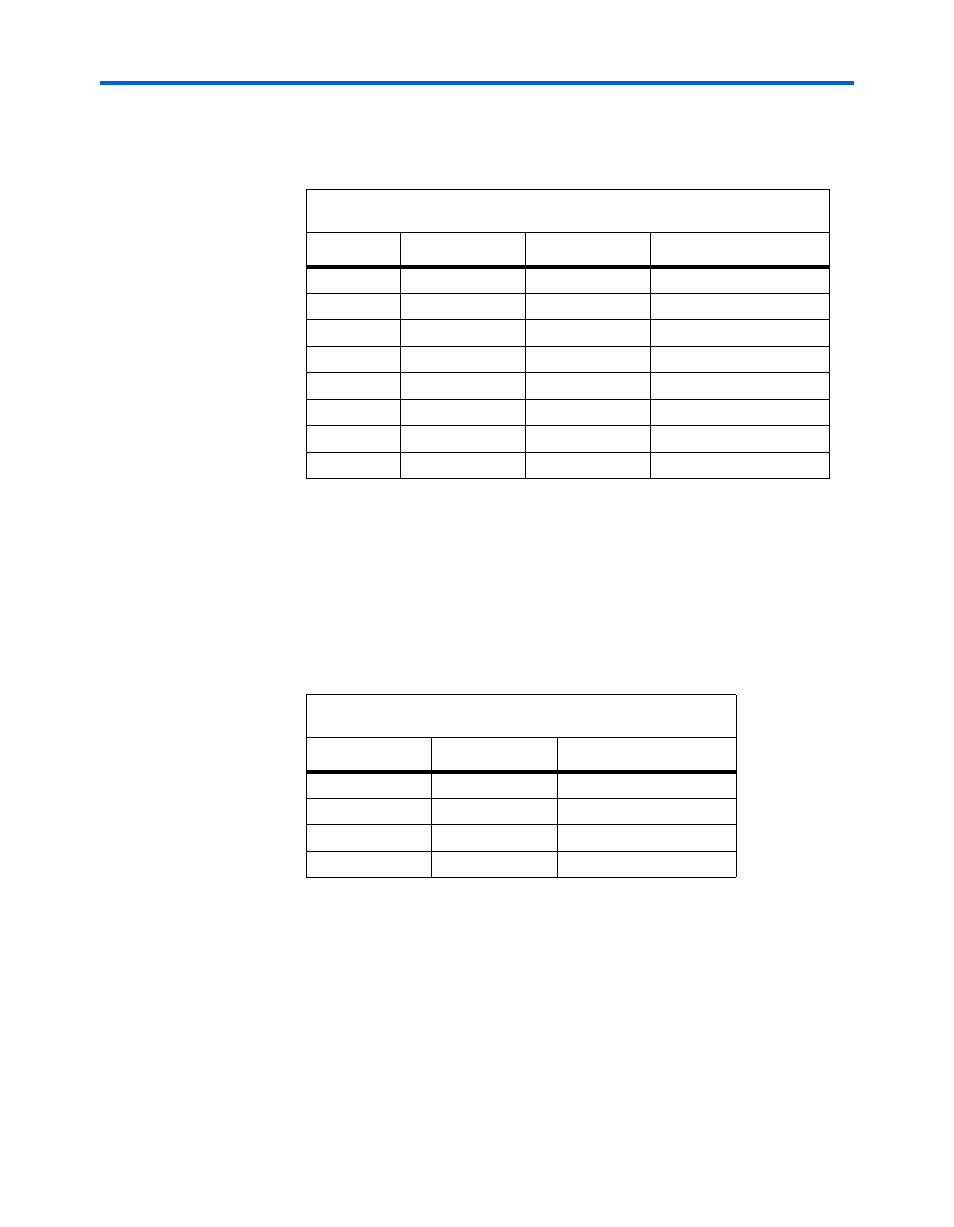

Table 2–17. Test Point Pin Table

Test Point

FPGA Pin

CPLD Pin

Board Net Name

TP1

D19

75

pld_user0

TP2

C19

76

pld_user1

TP3

A20

77

pld_user2

TP4

B20

78

pld_user3

TP5

K16

79

pld_user4

TP6

J16

80

pld_user5

TP7

K17

81

pld_user6

TP8

J18

83

pld_user7

Table 2–18. EPCS64 Pin Table

FPGA Pin

U69 Pin

Board Net Name

N6

16

pld_dclk

N3

8

pld_data0

D3

7

pld_cs_n

E3

15

pld_asdo