Mictor connector (j25), Mictor connector (j25) –29 – Altera Nios Development Board Cyclone II Edition User Manual

Page 41

Altera Corporation

Reference Manual

2–29

May 2007

Nios Development Board Cyclone II Edition

Board Components

Mictor

Connector (J25)

The Mictor connector (J25) can be used to transmit up to 27 high-speed

I/O signals with very low noise via a shielded Mictor cable. J25 can be

used as a debug port for the Nios II processor or as a general-purpose I/O

connector to the FPGA. Twenty five of the Mictor connector signals are

used as data, and two signals are used as clock input and clock output.

Most pins on J25 connect to I/O pins on the FPGA (U62). For systems that

do not use the Mictor connector for debugging the Nios II processor, any

on-chip signals can be routed to I/O pins and probed at J25. External

scopes and logic analyzers can connect to J25 and analyze a large number

of signals simultaneously.

f

For details on Nios II debugging products that use the Mictor connector,

see www.altera.com.

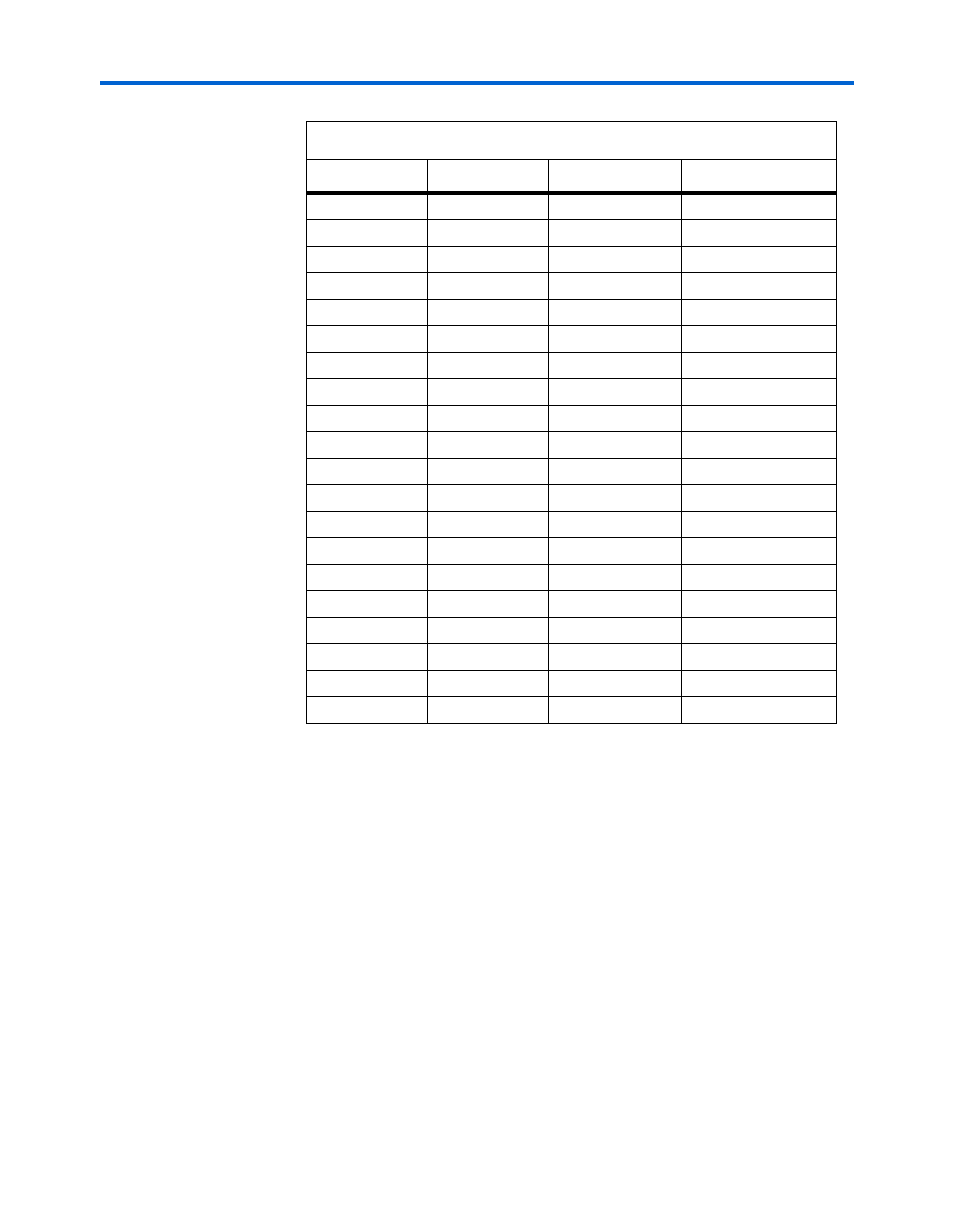

T20

43

JH1

pmc _par

W26

13

JH1

pmc_clk

U24

39

JH2

pmc_perr_n

U23

42

JH2

pmc_serr_n

R25

37

JH1

pmc_devsel_n

P24

38

JH2

pmc_stop_n

P23

36

JH1

pmc_irdy_n

M20

4

JH1

pmc_inta_n

Y14

5

JH1

pmc_intb_n

AA13

6

JH1

pmc_intc_n

Y13

9

JH1

pmc_intd_n

G22

13

JH2

pmc_reset_n

N24

33

JH1

pmc_frame_n

N23

35

JH2

pmc_trdy_n

M25

25

JH2

pmc_idsel

M24

16

JH1

pmc_gnt_n

N20

17

JH1

pmc_req_n

K26

40

JH1

pmc_lock_n

K25

47

JH2

pmc_m66en

AE15

64

JH1

pmc_req64_n

Table 2–15. PMC Connector Pin Table (Continued)

FPGA Pin

JH1 & JH2 Pin

Connector

Board Net Name