Flash memory (u5), Flash memory (u5) –11 – Altera Nios Development Board Cyclone II Edition User Manual

Page 23

Altera Corporation

Reference Manual

2–11

May 2007

Nios Development Board Cyclone II Edition

Board Components

Flash Memory

(U5)

U5 is an 8-bit, 16 Mbyte AMD flash memory device connected to the

FPGA. Depending on the board revision, the part number is

AM29LV128M or S29GL128M10TFIR1. Refer to

for connections

between the FPGA and the flash memory chip. U5 can be used for two

purposes:

1.

A Nios II embedded processor implemented on the FPGA can use

the flash memory as general-purpose memory and non-volatile

storage.

2.

The flash memory can hold FPGA configuration data that is used by

the configuration controller to load the FPGA at power-up. Refer to

“Configuration Controller Device (U3)” on page 2–33

for related

information.

A Nios II processor design in the FPGA can identify the 16 Mbyte flash

memory in its address space, and can program new data (either new

FPGA configuration data, Nios II software, or both) into flash memory.

The Nios II development software includes subroutines for writing and

erasing flash memory.

1

The flash memory device shares address and data connections

with the Ethernet MAC/PHY device.

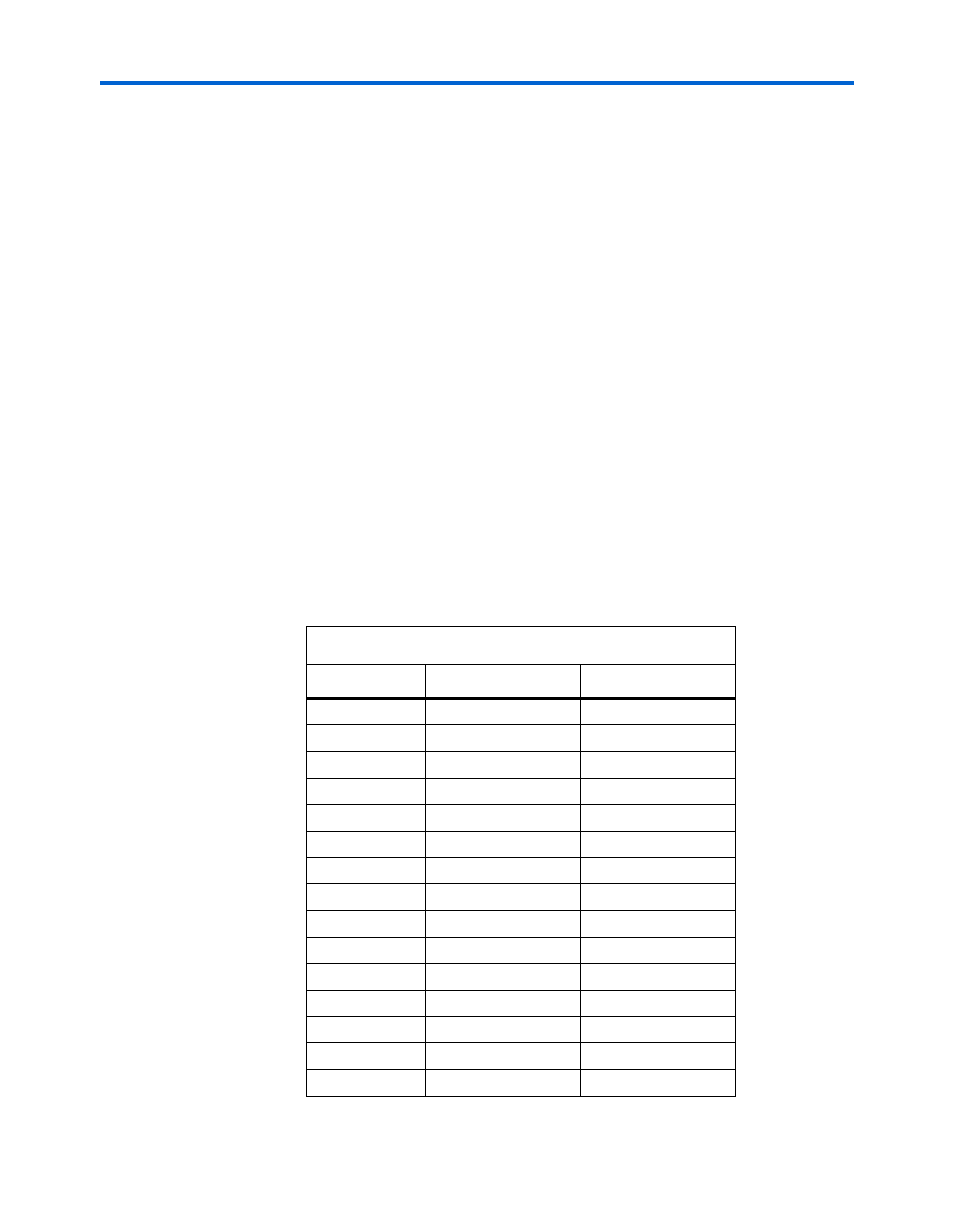

Table 2–8. Flash Memory Pin Table

FPGA Pin

U5 Pin

Board Net Name

F9

51

fe_a0

H8

31

fe_a1

D11

26

fe_a2

E8

25

fe_a3

B14

24

fe_a4

A14

23

fe_a5

F14

22

fe_a6

G14

21

fe_a7

F13

20

fe_a8

G13

10

fe_a9

C15

9

fe_a10

B15

8

fe_a11

B16

7

fe_a12

C16

6

fe_a13

D15

5

fe_a14