Cyclone ii ep2c35 device (u62), Cyclone ii ep2c35 device (u62) –3 – Altera Nios Development Board Cyclone II Edition User Manual

Page 15

Altera Corporation

Reference Manual

2–3

May 2007

Nios Development Board Cyclone II Edition

Board Components

The sections that follow describe each component in detail.

Cyclone II

EP2C35 Device

(U62)

U62 is a Cyclone II FPGA in a 672-pin FineLine BGA

®

package.

Depending on the board revision, the part number is EP2C35F672C5 or

EP2C35F672C5N.

lists the device features.

1

Preproduction builds of the Nios Development Board, Cyclone

II Editon have an EP2C35F6728ES device.

SW9

Factory Config button

Push-button switch to reconfigure the FPGA with the

factory-programmed reference design.

SW10

Reset, Config

Push-button switch to reset the board.

LED0 – LED3, LED6

Configuration status LEDs

LEDs that display the current configuration status of

the FPGA.

Clock Circuitry

Y2

Oscillator

50 MHz clock signal driven to FPGA.

J4

External clock input

Connector to FPGA clock pin.

Power Supply

J26

DC power jack

16V DC unregulated power source.

D34

Bridge rectifier

Power rectifier allows for center-negative or center-

positive power supplies.

J28, J29, J30, J33 (and

more)

Optional Power Supply

External power supply can be connected for high-

current applications.

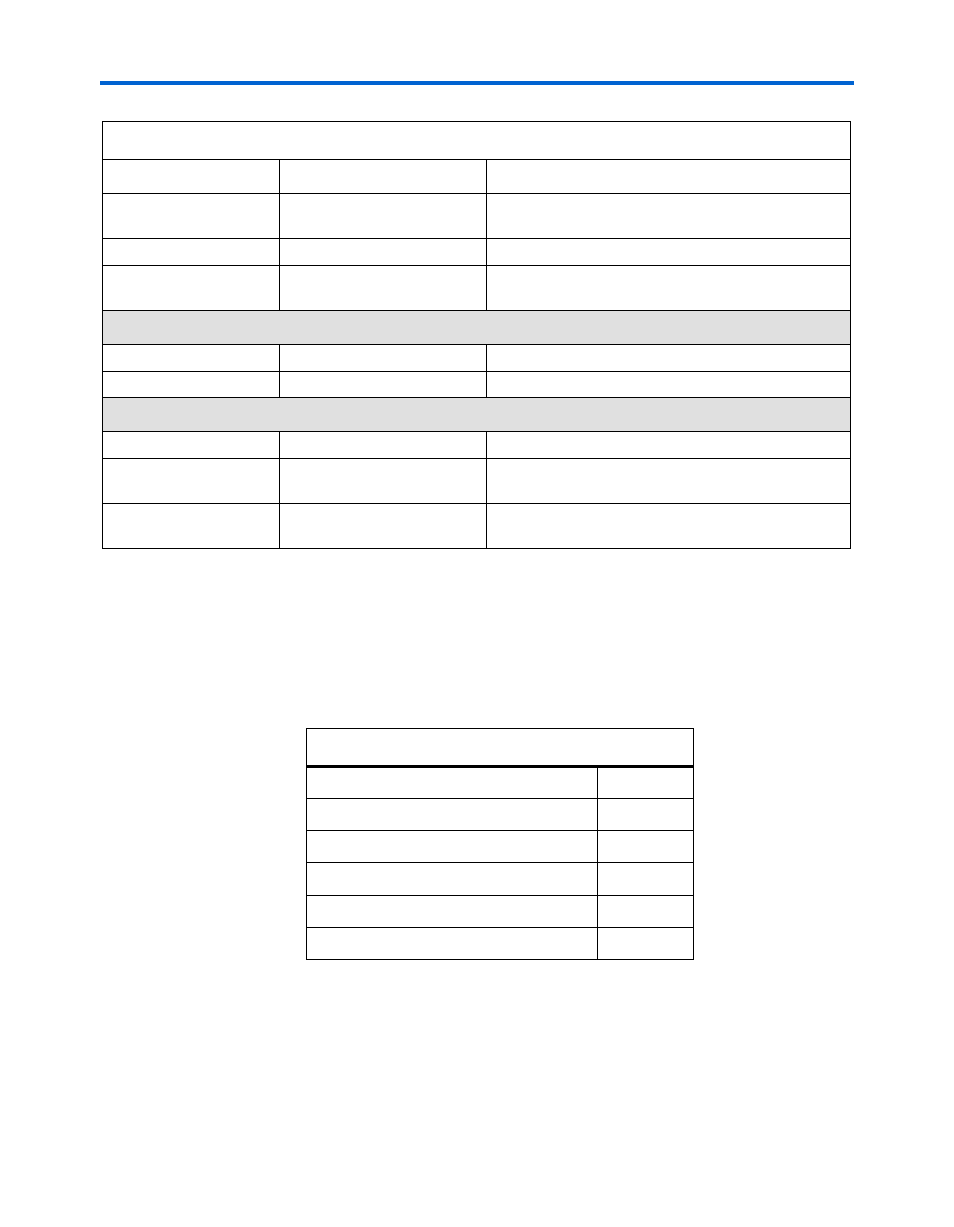

Table 2–1. Nios Development Board, Cyclone II Edition Components & Interfaces (Continued)

Board Designation

Name

Description

Table 2–2. Cyclone II EP2C35 Device Features

LEs 33,216

M4K Memory Blocks

105

Total RAM Bits

483,840

Embedded 18x18 Multiplier Blocks

35

PLLs

4

User I/O Pins

475