Ethernet mac/phy (u4) & rj45 connector (rj1), Ethernet mac/phy (u4) & rj45 connector (rj1) –13 – Altera Nios Development Board Cyclone II Edition User Manual

Page 25

Altera Corporation

Reference Manual

2–13

May 2007

Nios Development Board Cyclone II Edition

Board Components

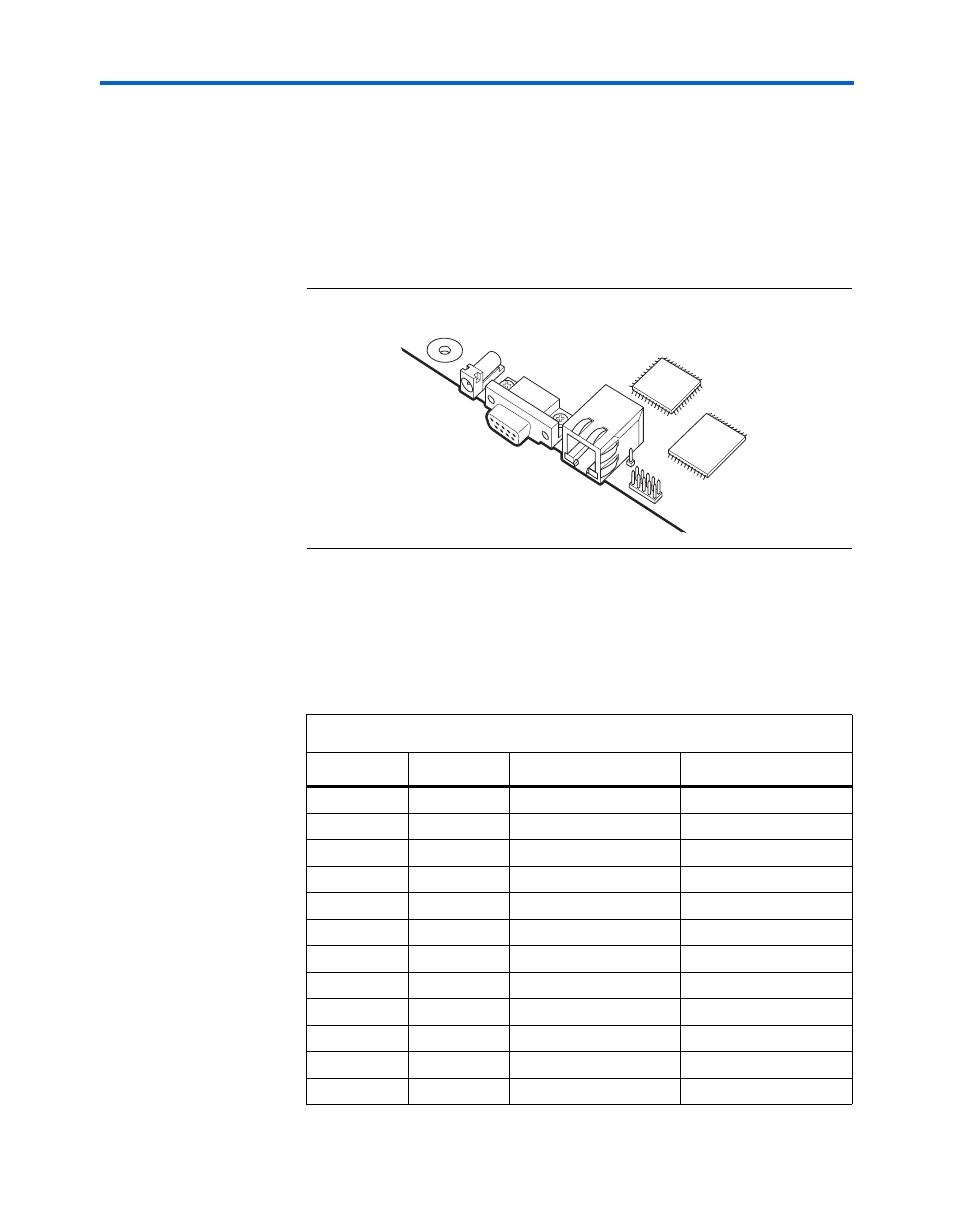

Ethernet

MAC/PHY (U4) &

RJ45 Connector

(RJ1)

The LAN91C111 chip (U4) is a 10/100 Ethernet media access control and

physical interface (MAC/PHY) chip. The control pins of U4 are

connected to the FPGA so that Nios II systems can access Ethernet

networks via the RJ-45 connector (RJ1) as shown in

. The

Nios II development tools include hardware and software components

that allow Nios II processor systems to communicate with the

LAN91C111 Ethernet device.

Figure 2–4. Ethernet RJ-45 Connector

Refer to

for connections between the FPGA and the MAC/PHY

device.

1

The Ethernet MAC/PHY device shares both address and data

connections with the flash memory.

Table 2–9. Ethernet MAC/PHY Pin Table

FPGA Pin

U4 Pin

Pin Function

Board Net Name

(1)

E26

41

Address Enable

enet_aen

J17

43

Synchronous Ready

enet_srdy_n

F18

40

VL Bus Access

enet_vlbus_n

G18

45

Local Device

enet_ldev_n

D18

38

IO Char Ready

enet_iochrdy

E18

37

Address Strobe

enet_ads_n

A19

42

Local Bus Clock

enet_lclk

B19

46

Ready/Return

enet_rdyrtn_n

D20

35

Bus Cycle

enet_cycle_n

D14

36

Write/Read

enet_w_r_n

Y15

34

Bus Chip Select

enet_datacs_n

AA15

29

Interrupt

enet_intr0

RJ1

U4