Pmc connector (jh1 & jh2), Pmc connector (jh1 & jh2) –26 – Altera Nios Development Board Cyclone II Edition User Manual

Page 38

2–26

Reference Manual

Altera Corporation

Nios Development Board Cyclone II Edition

May 2007

Board Components

f

For more information on the CompactFlash connector (CON3), see

www.compactflash.org

and www.molex.com.

PMC Connector

(JH1 & JH2)

The PCI mezzanine card (PMC) connector, formed by JH1 and JH2,

allows Nios II systems in the FPGA to interface to daughter cards using

the standard 32-bit PMC form factor. Refer to

. The PMC

connector is capable of 33MHz and 66 MHz, and is configured as the PMC

host.

w

Before connecting a daughter card to the PMC connector, the

FPGA must first be configured with a design that includes a

PMC interface. Damage to either the FPGA or daughter card can

result if the FPGA is not configured correctly.

The factory-programmed Nios II reference design does not include a

PMC interface.

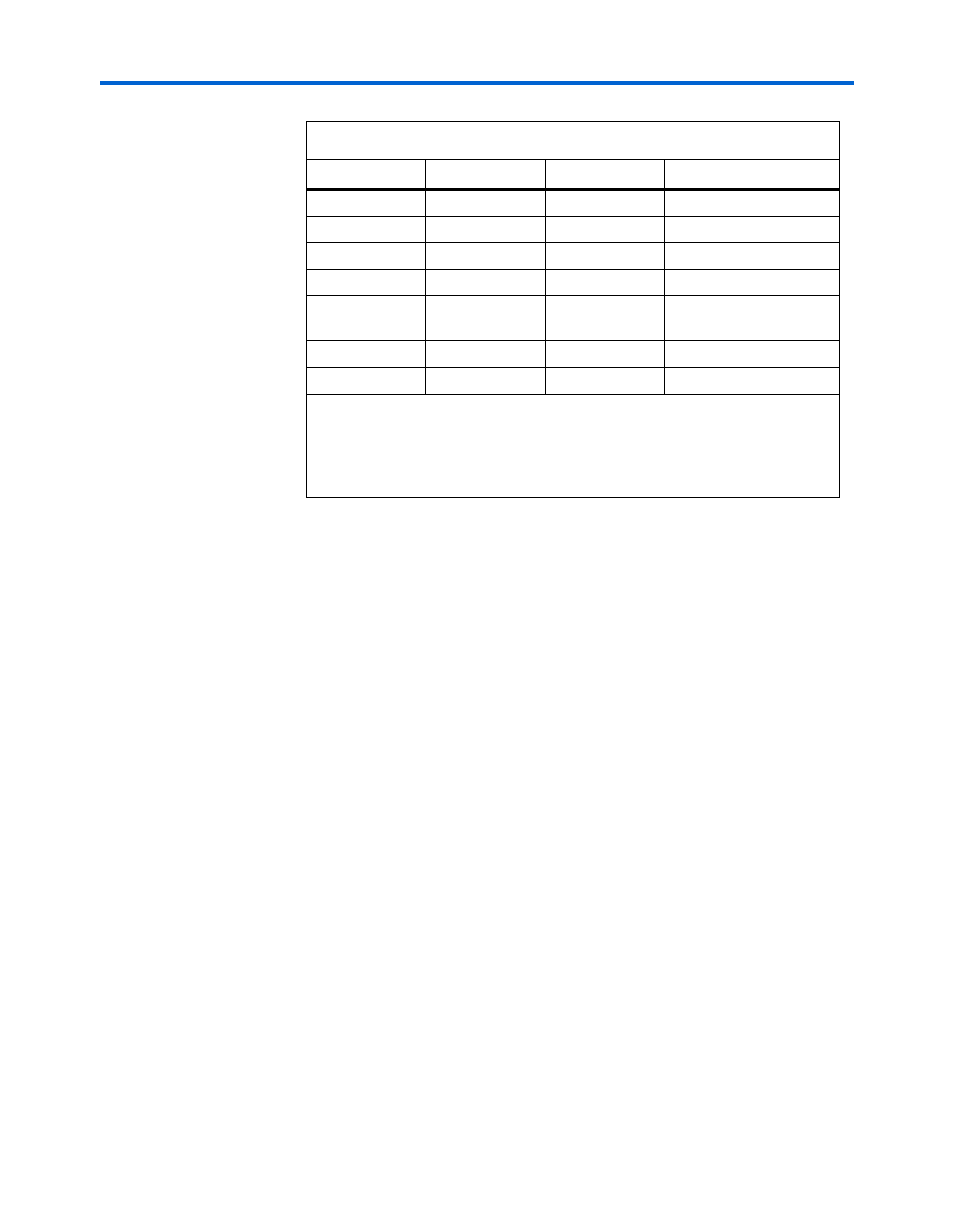

V23

43

INPACK_n

proto1_io39

Y22

44

REG_n

proto1_io40

W16

32

CS1_n

cf_cs_n

AE16

9

ATA_SEL_n

cf_atasel_n

AD16

5

Power supply

enable

cf_power

(2)

W15

26

CD1_n

cf_present_n

56 (U3)

41

RESET#

proto1_RESET_n

(3)

Notes to

(1)

Nets proto_io16, proto_io20, and proto_io21 do not connect to CON3.

(2)

The FPGA I/O pin controls a power MOSFET that supplies 5V VCC to this net.

(3)

proto1_RESET_n is driven by the EPM7256AE configuration controller device

(U3).

Table 2–13. CompactFlash Pin Table (Continued)

FPGA Pin

CON3 Pin

Pin Function

Board Net Name

(1)