Altera SDI Audio IP Cores User Manual

Page 34

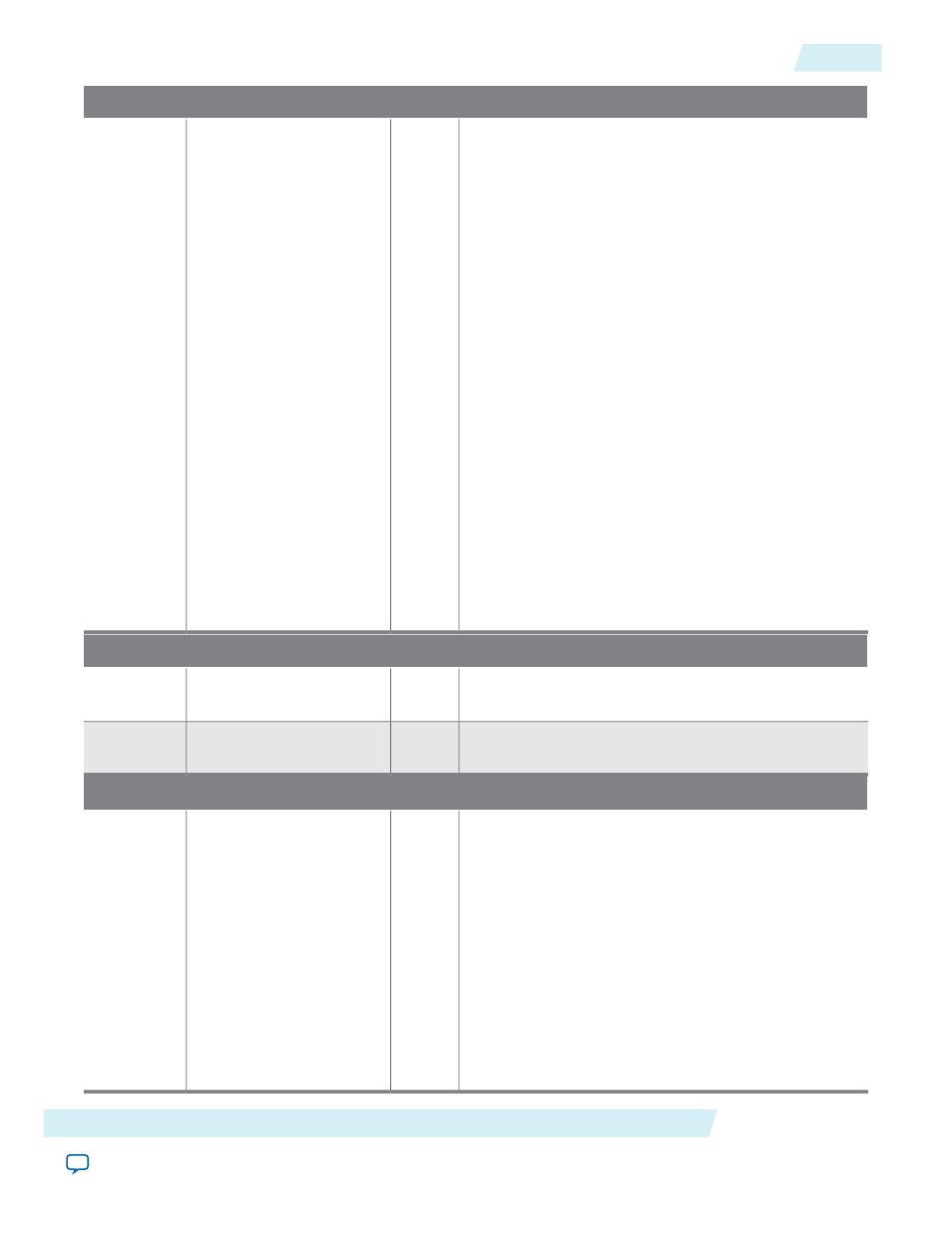

Video Status Register

Reports the detected video input standard.

• Bits[7:5] = Picture structure code. Defined values for

picture structure code are:

• 001b = 486 or 576 line SD-SDI

• 100b = 720 line HD-SDI

• 101b = 1080 line HD-SDI

• 010b = 1080 line 3G-SDI

• 011b = 1080 line 3GA-SDI

• 110b = 720 line 3GA-SDI

• 111b = 720 line 3GB-SDI

• Bit[4] = 0b—Interlace or segmented frame,

1b—Progressive.

• Bits[3:0] = Frame rate code. Defined values for frame

rate code (in Hz) are:

• 0010b = 23.97

• 0011b = 24

• 0101b = 25

• 0110b = 29.97

• 0111b = 30

• 1001b = 50

• 1010b = 59.94

• 1011b = 60

RO

Active channel

7:0

SD EDP Control Register

Enables the embedding of SD-SDI Extended Data

Packets (EDP) for each audio group.

RW

Enable SD EDP

3:0

Enables the embedding of SD-SDI Audio Control

Packets (ACP) for each audio group.

RW

Enable SD ACP

7:4

Channel Status Control Register

When set to 00b, the core keeps the existing channel

status data.

When set to 01b, the core replaces the channel status

data with default values.

When set to 10b, the core replaces the data with the

contents of the appropriate channel status RAM.

The following bits correspond to the number of audio

groups you specify:

• Bit [1:0] = Audio group 1

• Bit [3:2] = Audio group 2

• Bit [5:4] = Audio group 3

• Bit [7:6] = Audio group 4

RW

CS mode select

7:0

Altera Corporation

SDI Audio IP Registers

5-3

SDI Audio Embed Registers

UG-SDI-AUD

2014.06.30