Sdi audio extract ip core, Sdi audio extract ip core -4 – Altera SDI Audio IP Cores User Manual

Page 13

Description

Value

Parameter

Turn on to include the Avalon-MM control interface.

When you turn on this parameter, the register interface signals

appear at the top level. Otherwise, the direct control interface

signals appear at the top level.

On or Off

Include Avalon-

MM control

interface

Related Information

on page 4-1

SDI Audio Extract IP Core

The SDI Audio Extract IP core accepts the SD-, HD-, and 3G-SDI from the SDI IP cores and extracts one

channel pair of embedded audio.

The format of the embedded audio is in accordance with the following standards:

• SMPTE272M-ABCD standard for SD-SDI

• SMPTE299M standard for HD-SDI

• SMPTE299M standard for 3G-SDI (provisional)

If you are extracting more than one channel pair, you must use multiple instances of the component. This

IP core supports AES audio format for 48-kHz sampling rate.

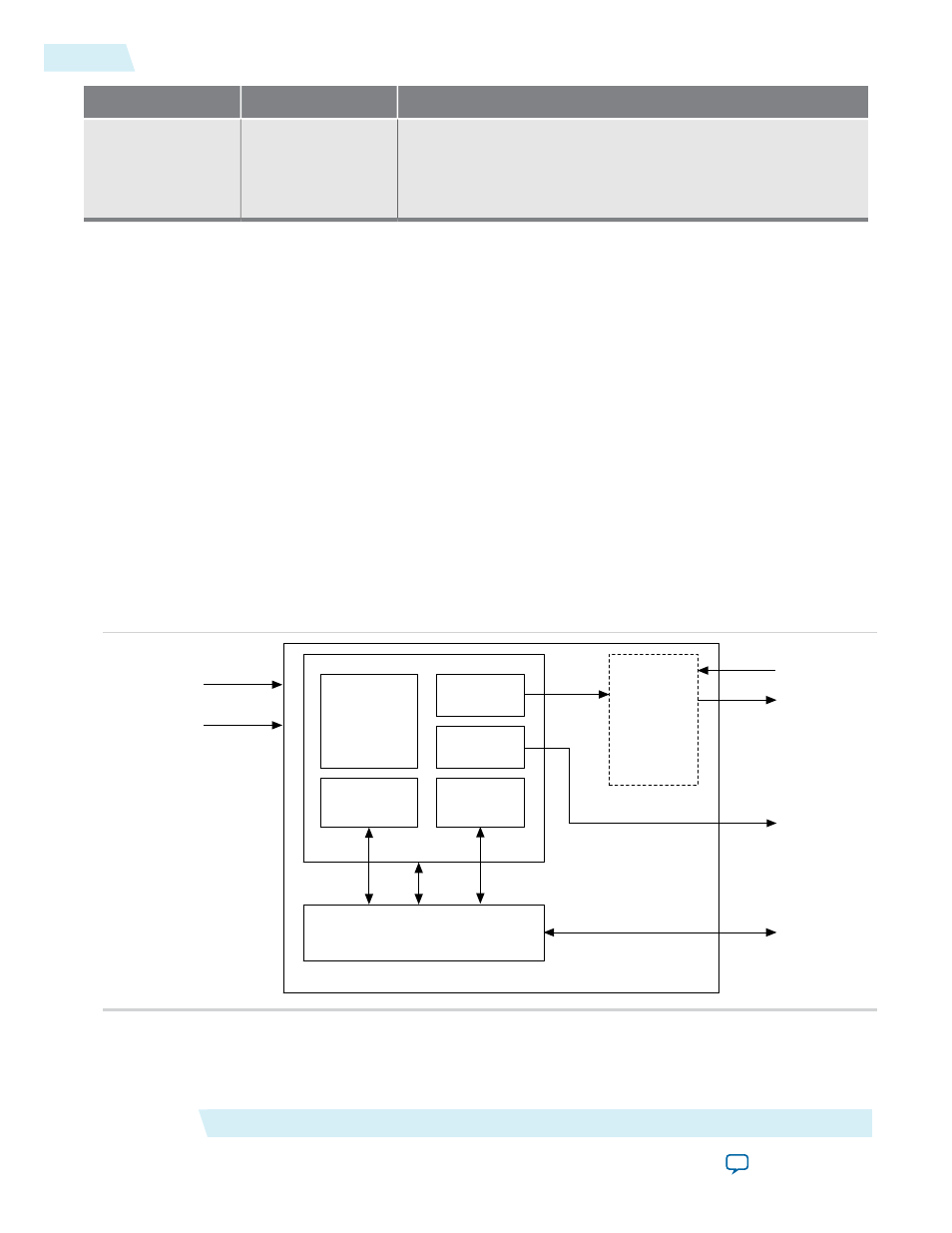

This figure shows a block diagram of the SDI Audio Extract IP core.

Figure 3-2: SDI Audio Extract IP Core Block Diagram

Sample FIFO

Clock Recovery

Audio Extract or Audio Extract with Avalon

Avalon-MM

48 KHz Clock

Core

Error Detection

Packet Find

and

Extract

AES

to

Avalon-ST Audio

(Audio Extract

with Avalon Only)

Channel

Status RAM

Register Interface

aud_clk

internal AES

Avalon-ST

Audio

vid_clk

SD/HD/3G-SDI

The SDI Audio Extract IP core consists of the following components:

• An audio extraction core

SDI Audio IP Functional Description

Altera Corporation

UG-SDI-AUD

SDI Audio Extract IP Core

3-4

2014.06.30