Altera SDI Audio IP Cores User Manual

Page 23

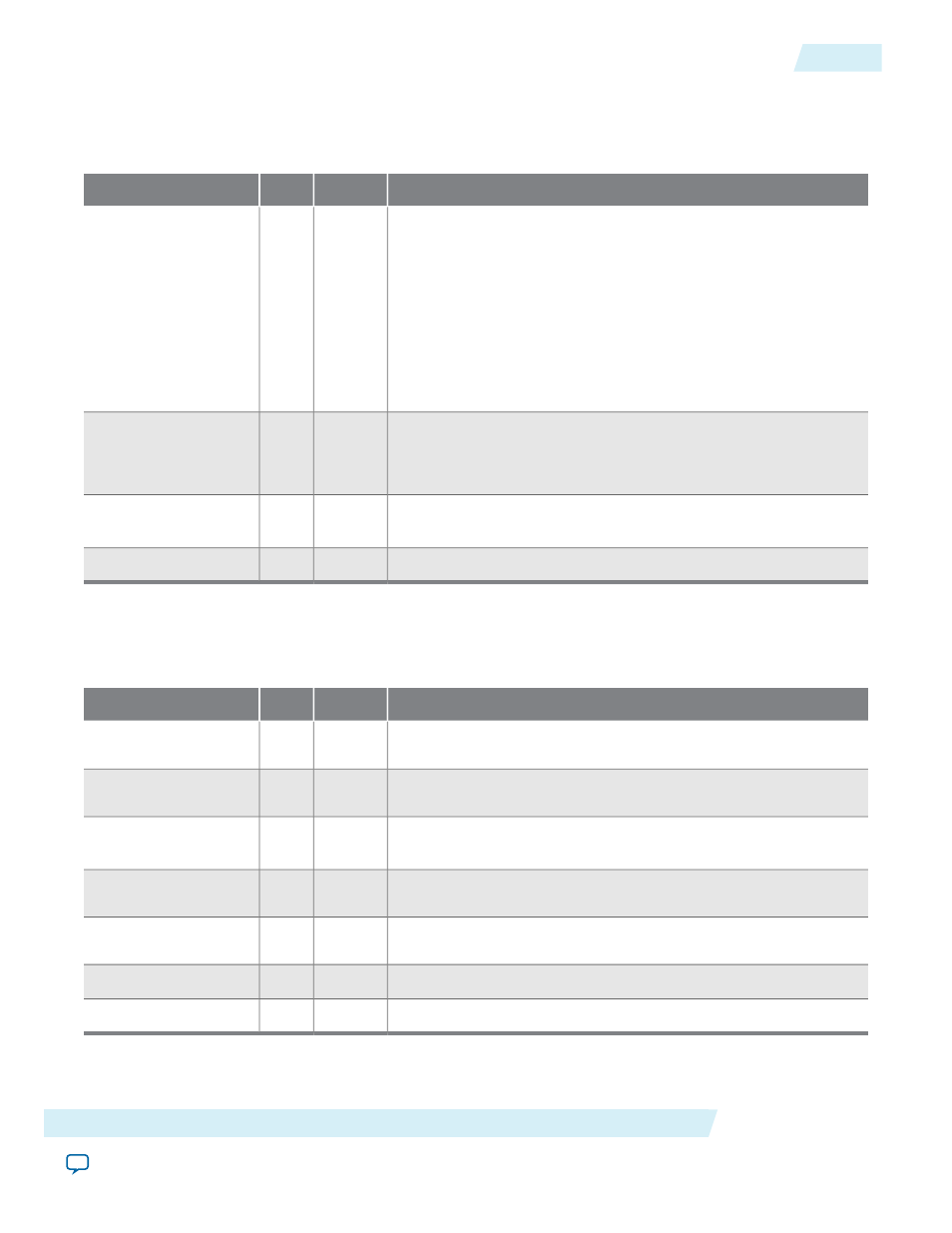

This table lists the audio input signals.

Table 4-3: SDI Audio Embed Audio Input Signals

N

is the number of audio group.

Description

Direction

Width

Signal

Set this clock to 3.072 MHz that is synchronous to the extracted

audio. In asynchronous mode, set this to any frequency above 3.072

MHz. Altera recommends that you set this clock to 50 MHz.

For SD-SDI inputs, this mode of operation limits the core to

embedding audio that is synchronous to the video. For HD-SDI

inputs, this clock must either be generated from the optional 48

Hz output or the audio must be synchronous to the video.

Set exclusive clock group to

aud_clk

and

vid_clk

to prevent

unstable or flickering image.

Input

[2N–1:0]

aud_clk

Assert this data enable signal to indicate valid information on the

aud_ws

and

aud_data

signals.

In synchronous mode, the core ignores this signal.

Input

[2N–1:0]

aud_de

Assert this word select signal to provide framing for deserialization

and to indicate left or right sample of channel pair.

Input

[2N–1:0]

aud_ws

Internal AES data signal from the AES input module.

Input

[2N–1:0]

aud_data

This table lists the Avalon-ST audio signals when you instantiate the SDI Audio Embed IP core in Qsys.

Table 4-4: SDI Audio Embed Avalon-ST Audio Signals

n

is the number of audio channels, the value starts from from 0 to

n

-1.

Description

Direction

Width

Signal

Clocked audio clock. All the audio input signals are synchronous

to this clock.

Input

[0:0]

aud(n)_clk

Avalon-ST ready signal. Assert this signal when the device is able

to receive data.

Output

[0:0]

aud(n)_ready

Avalon-ST valid signal. The core asserts this signal when it receives

data.

Input

[0:0]

aud(n)_valid

Avalon-ST start of packet signal. The core asserts this signal when

it is starting a new frame.

Input

[0:0]

aud(n)_sop

Avalon-ST end of packet signal. The core asserts this signal when

it is ending a frame.

Input

[0:0]

aud(n)_eop

Avalon-ST select signal. Use this signal to select a specific channel.

Input

[7:0]

aud(n)_channel

Avalon-ST data bus. This bus transfers data.

Input

[23:0]

aud(n)_data

This table lists the register interface signals. The register interface is a standard 8-bit wide Avalon-MM slave.

Altera Corporation

SDI Audio IP Interface Signals

4-3

SDI Audio Embed Signals

UG-SDI-AUD

2014.06.30