Clock divider, Ripple clock – Altera HardCopy II Clock Uncertainty Calculator User Manual

Page 29

Altera Corporation

3–3

HardCopy II Clock Uncertainty Calculator User Guide

Design Case Exceptions

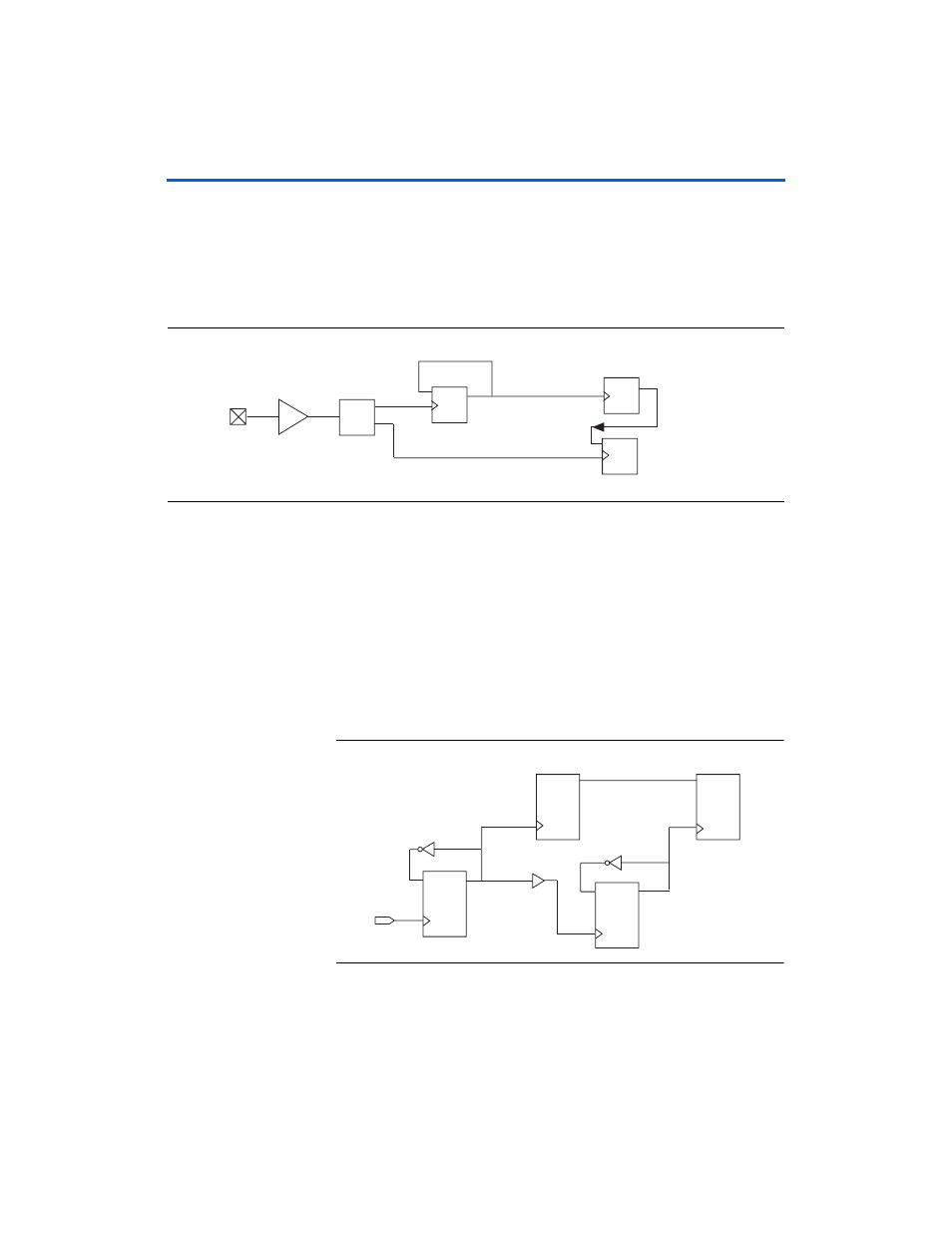

Clock Divider

shows an example of a clock divider for intra-clock transfer, in

which

CLK1 is accounted for in the clock uncertainty calculator, but not

CLK2. You should add 25 ps to both the setup and hold clock uncertainty

values.

Figure 3–4. Clock Divider for Intra-Clock Transfer

Ripple Clock

shows a ripple clock as an intra-clock transfer example. A

ripple clock is similar to a divided clock, but uses a different calculation

to account for extra clock uncertainty value.

CLK0 is accounted for by the clock uncertainty calculator, but not CLK1

and

CLK2. You need to add 25 ps uncertainty for the CLK1 network and

also add 25 ps uncertainty for the

CLK2 network. Therefore, you should

add 50 ps on both setup and hold clock uncertainty for the example

shown in

.

Figure 3–5. Ripple Clock for Intra-Clock Transfer

PLL

INBUF

Source

Clock

Destination

Clock

Source

Register

Destination

Register

CLK1

CLK2

CLK3

CLK1

clk_a

clk_b

CLK1

CLK0

reg_c

reg_d

CLK2