Chapter 3. design case exceptions – Altera HardCopy II Clock Uncertainty Calculator User Manual

Page 27

Altera Corporation

3–1

Chapter 3. Design Case

Exceptions

Multiple Clock

Uncertainty on a

Single Clock

Transfer

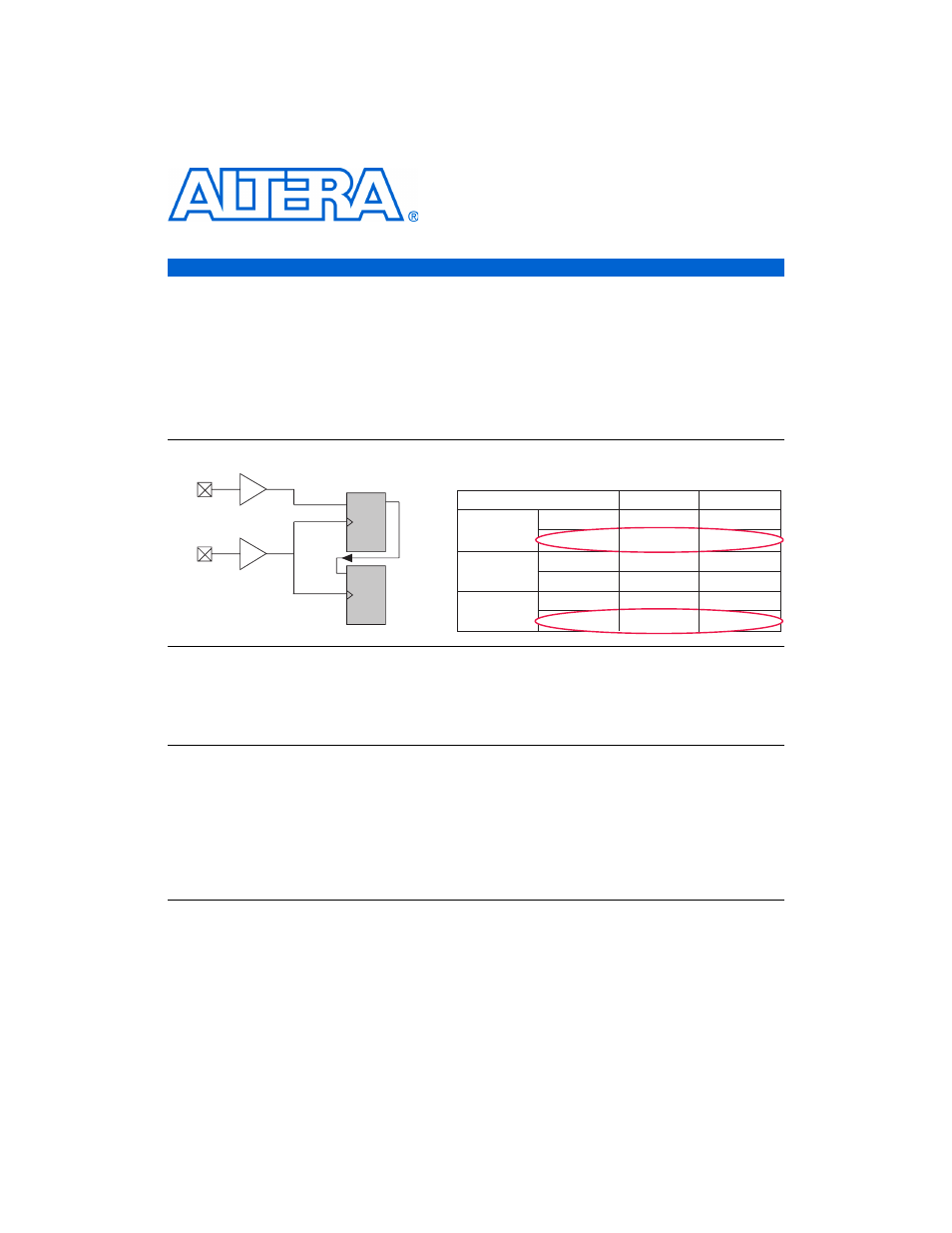

In real designs, there are some special cases for calculating clock

uncertainty values that require extra steps.

shows a design with both I/O transfer and intra-clock

transfer. In this case, there are two possible clock uncertainties (I/O and

data paths) for the same clock transfer.

Figure 3–1. Circuit with Intra-Clock Transfer and I/O Interface

To set the clock uncertainty constraints correctly, you should create a

virtual clock for the circuit. The following code example shows the SDC

used to constrain the design, as shown in

:

Example 3–1. SDC Constraints for i/O

create_clock –name CLK1 –period 10 [get_ports {CLK1}]

create_clock –name VIRTUAL_CLK –period 10

set_input_delay –max –clock VIRTUAL_CLK 8.00 [get_ports {DIN1}]

set_input_delay –min –clock VIRTUAL_CLK 2.00 [get_ports {DIN1}]

set_clock_uncertainty –from CLK1 –to CLK1 –setup 0.200

set_clock_uncertainty –from CLK1 –to CLK1 –hold 0.050

set_clock_uncertainty –from VIRTUAL_CLK1 –to CLK1 –setup 0.180

set_clock_uncertainty –from VIRTUAL_CLK1 –to CLK1 –hold 0.180

Clock Transfer Type

Setup CU (ps)

Hold CU (ps)

Intra-Clock

Inter-Clock

I/O Interface

With PLL

Without PLL

With PLL

With PLL

330

350

150

50

330

350

150

100

Without PLL

200

50

Without PLL

180

180

DIN1

CLK1

INBUF