Various clock structures, Clock gated in core, Various clock structures –2 – Altera HardCopy II Clock Uncertainty Calculator User Manual

Page 28

3–2

Altera

Corporation

HardCopy II Clock Uncertainty Calculator User Guide

Various Clock Structures

Various Clock

Structures

When a clock is generated in the core, additional clock uncertainty may

be introduced by the additional routing. The HardCopy

®

II Clock

Uncertainty Calculator supports the following clock structures:

■

AND and MUX gated clocks

■

Clock divider

■

Ripple clock

■

Multiple clock networks

■

Multi-cycle clock

For each global and local clock network added to any of the examples in

, clock uncertainty values should be increased by 25 ps. The

following examples are for intra-clock transfer with PLL; the same rules

apply for inter-clock transfer and I/O transfers, as well as for all cases not

involving PLLs.

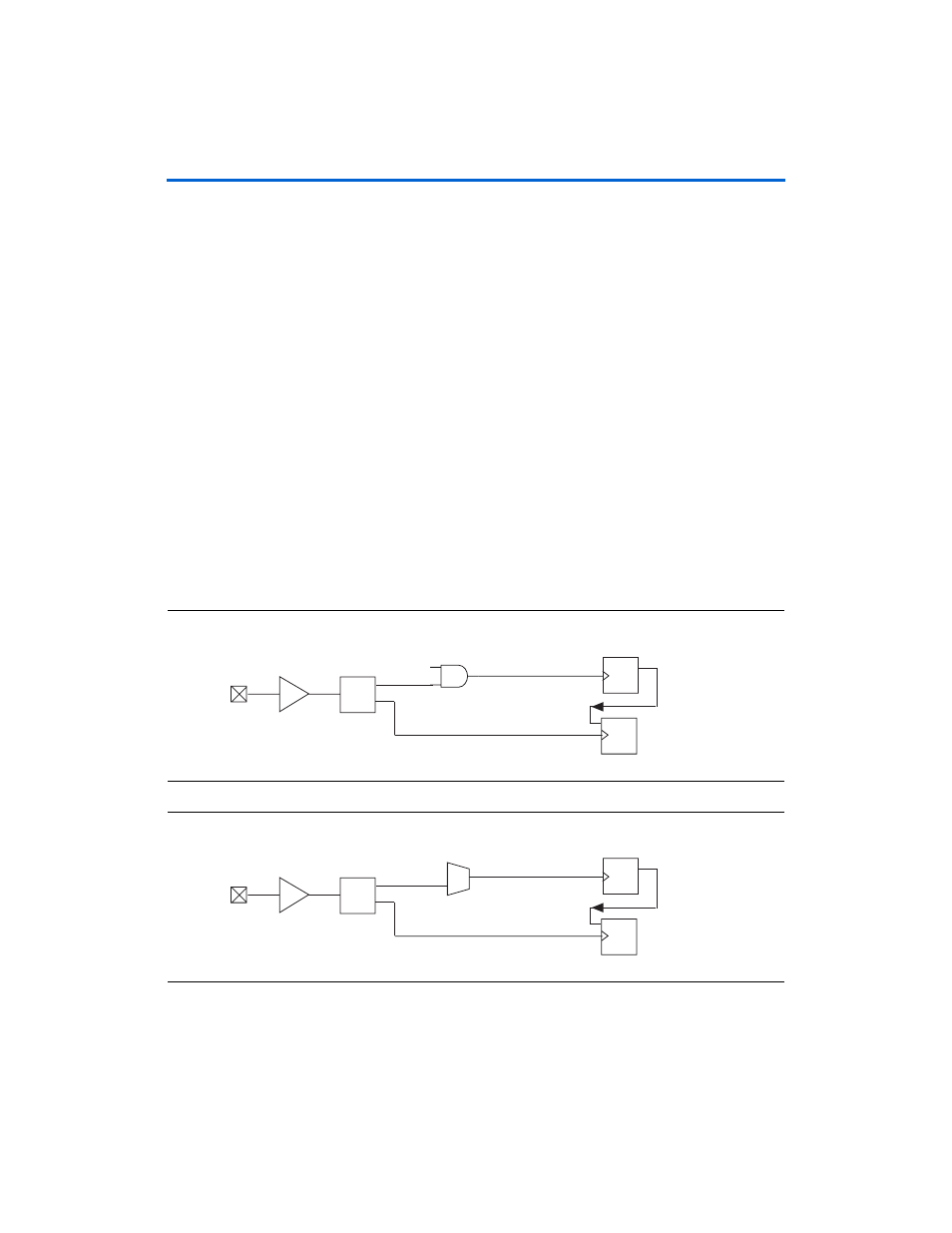

Clock Gated in Core

, the source register is driven by an AND or MUX

gated clock,

CLK2. Because the clock uncertainty calculator does not

account for the clock network on

CLK2, you must add 25 ps on both the

setup and hold clock uncertainty values.

Figure 3–2. AND-Gated Clock for Intra-Clock Transfer

Figure 3–3. MUX-Gated Clock for Intra-Clock Transfer

PLL

INBUF

Source

Clock

Destination

Clock

Source

Register

Destination

Register

CLK1

CLK2

CLK3

PLL

INBUF

Source

Clock

Destination

Clock

Source

Register

Destination

Register

CLK1

CLK2

CLK3