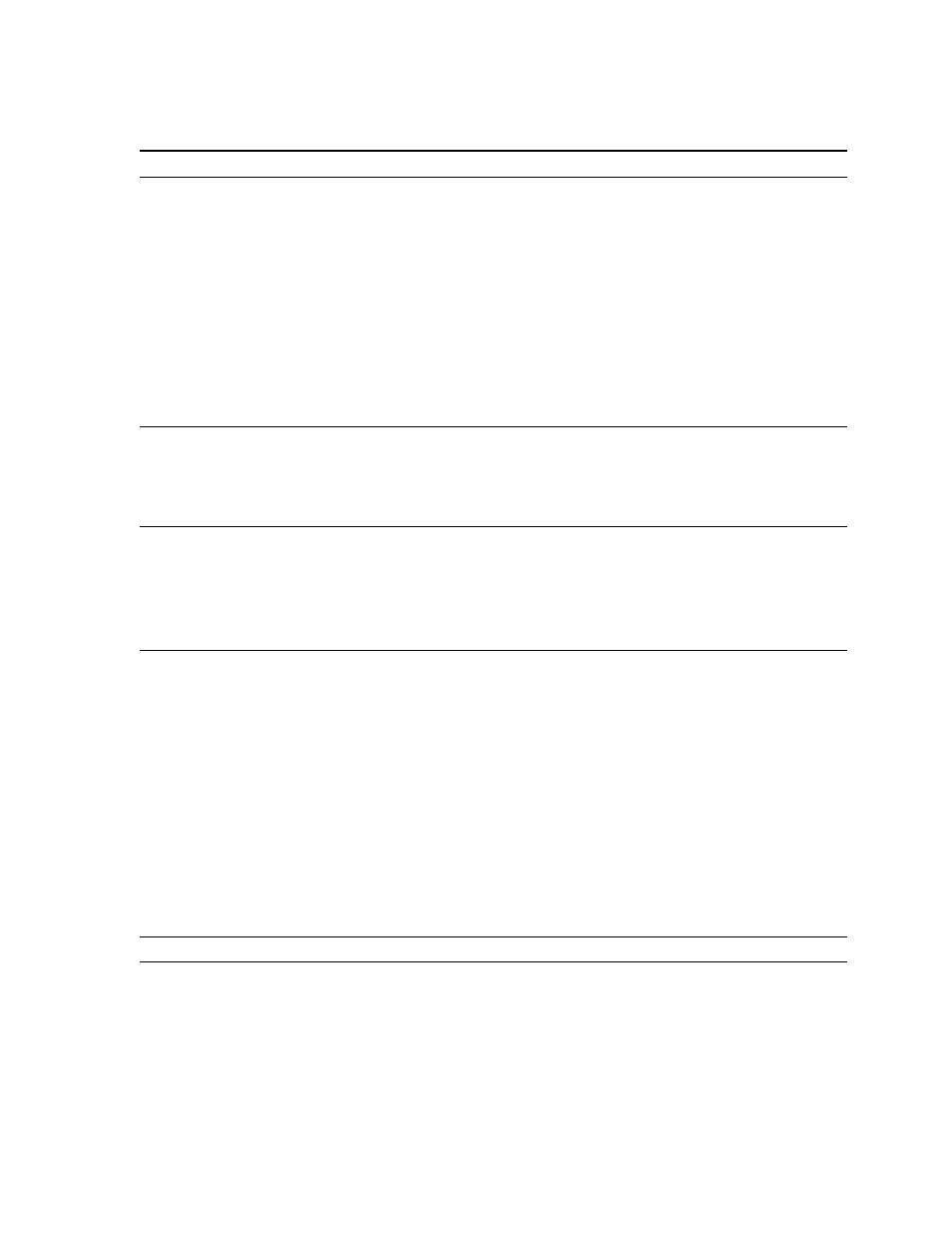

Ac characteristics – Compaq 21264 User Manual

Page 248

9–8

Electrical Data

Alpha 21264/EV67 Hardware Reference Manual

AC Characteristics

BcTagShared_H

B_DA_PP

BcTagInClk_H

400 ps

400 ps

NA

NA

1.0 V/ns

BcTagValid_H

B_DA_PP

BcTagInClk_H

400 ps

400 ps

NA

NA

1.0 V/ns

BcTagValid_H

B_DA_PP

BcTagOutClk_x

NA

NA

± 300 ps

45-55%

NA

BcTagDirty_H

B_DA_PP

38-63%

NA

BcTagShared_H

B_DA_PP

40-60%

NA

BcTagParity_H

B_DA_PP

BcTagOE_L

O_PP

BcTagWr_L

O_PP

BcTagInClk_H

I_DA

NA

NA

NA

NA

45-55%

BcTagOutClk_x

O_PP

EV6Clk_x

NA

NA

± 400 ps

IRQ_H[5:0]

I_DA

DCOK_H

10 ns

11

10 ns

NA

NA

100 mV/ns

Reset_L

12

I_DA

NA

NA

NA

NA

100 mV/ns

DCOK_H

13

I_DA

NA

NA

NA

NA

100 mV/ns

PllBypass_H

14

I_DA

NA

NA

NA

NA

100 mV/ns

ClkIn_x

15

I_DA_CLK

NA

NA

NA

40–60%

16

1.0 V/ns

FrameClk_x

17

I_DA_CLK

ClkIn_x

400 ps

400 ps

NA

NA

1.0 V/ns

EV6Clk_x

18

O_PP_CLK

ClkIn_x

NA

NA

±1.0 ns

YDiv±5%

NA

EV6Clk_x

19

Cycle Compression Specification: See Note 19

ClkFwdRst_H

I_DA

FrameClk_x

400 ps

400 ps

NA

NA

1.0 V/ns

SromData_H

I_DA

SromClk_H

2.0 ns

2.0 ns

NA

100 mV/ns

SromOE_L

O_OD

EV6Clk_x

NA

NA

± 2.0 ns

SromClk_H

20

O_OD

EV6Clk_x

NA

NA

± 7.0 ns

Tms_H

I_DA

Tck_H

2.0 ns

2.0 ns

NA

NA

100 mV/ns

Trst_L

21

I_DA

Tck_H

NA

NA

NA

NA

100 mV/ns

Tdi_H

I_DA

Tck_H

2.0 ns

2.0 ns

NA

NA

100 mV/ns

Tdo_H

O_OD

Tck_H

NA

NA

± 7.0 ns

NA

NA

Tck_H

I_DA

IEEE 1149.1 Port Freq. = 5.0

MHz Max.

NA

NA

NA

45-55%

100 mV/ns

TestStat_H

O_OD

EV6Clk_x

NA

NA

± 4.0 ns

NA

NA

1

The TSU specified for all clock-forwarded signal groups is with respect to the associated clock.

2

The TDH specified for all clock-forwarded signal groups is with respect to the associated clock.

3

The TSkew value applies only when the SYS_CLK_DELAY[0:1] entry in the Cbox WRITE_ONCE

chain (Table 5–24) is set to zero phases of delay between forwarded clock out and address/data.

4

The TSkew specified for SysData_L signals is only with respect to the associated clock.

5

These signals should be referenced to BcTagOutClk_x when measuring TSkew, provided that

BcTagOutClkl_x and BcDataOutClk_x have no programmed offset.

Table 9–13 AC Specifications (Continued)

Signal Name

Type

Reference Signal

TSU

1

TDH

2

TSkew

Duty Cycle

TSlew