2 data transfer commands (two cycles), Data transfer commands (two cycles), Data transfer command format – Compaq 21264 User Manual

Page 116: Ee section 4.7.7.2 f

4–28

Cache and External Interfaces

Alpha 21264/EV67 Hardware Reference Manual

System Port

The 21264/EV67 holds pending probe commands in a 8-entry deep probe queue. The

system must count the number of probes that have been sent and ensure that the probes

do not overrun the 21264/EV67 queue. The 21264/EV67 removes probes from the

internal probe queue when the probe response is sent.

The 21264/EV67 expects to hit in cache on a probe response, so it always fetches a

cache block from the Bcache on system probes. This can become a performance prob-

lem for systems that do not monitor the Bcache tags, so the 21264/EV67 provides Cbox

CSR PRB_TAG_ONLY[0], which only accesses Bcache tags for system probes. For a

Bcache hit, the 21264/EV67 retries the probe reference to get the associated data. In

this mode, the 21264/EV67 has a cache-hit counter that maintains some history of past

cache hits in order to fetch the data with the tag in the cases where streamed transac-

tions are being performed to the host processor.

4.7.7.2 Data Transfer Commands (Two Cycles)

Data transfer commands use a 2-cycle format on SysAddIn_L[14:0]. The SysDc[4:0]

field indicates success or failure for ChangeToDirty and MB commands, and error con-

ditions as shown in Table 4–24.

The pattern of data is controlled by the SysDataInValid_L and SysDataOutValid_L

signals. These signals are valid each cycle of data transfer, indicating any gaps in the

data cycle pattern. The SysDataInValid_L and SysDataOutValid_L signals are

described in Section 4.7.8.4. Table 4–23 shows the format of the data transfer com-

mand.

101

Invalid

110

Transition1

2

: Clean

⇒

Clean/Shared

Dirty

⇒

Dirty/Shared

111

Reserved

1

Transition3 is useful in nonduplicate tag systems that want to give writable status to the reader and do

not know if the block is clean or dirty.

2

Transition1 is useful in nonduplicate tag systems that do not update memory on ReadBlk hits to a

dirty block in another processor.

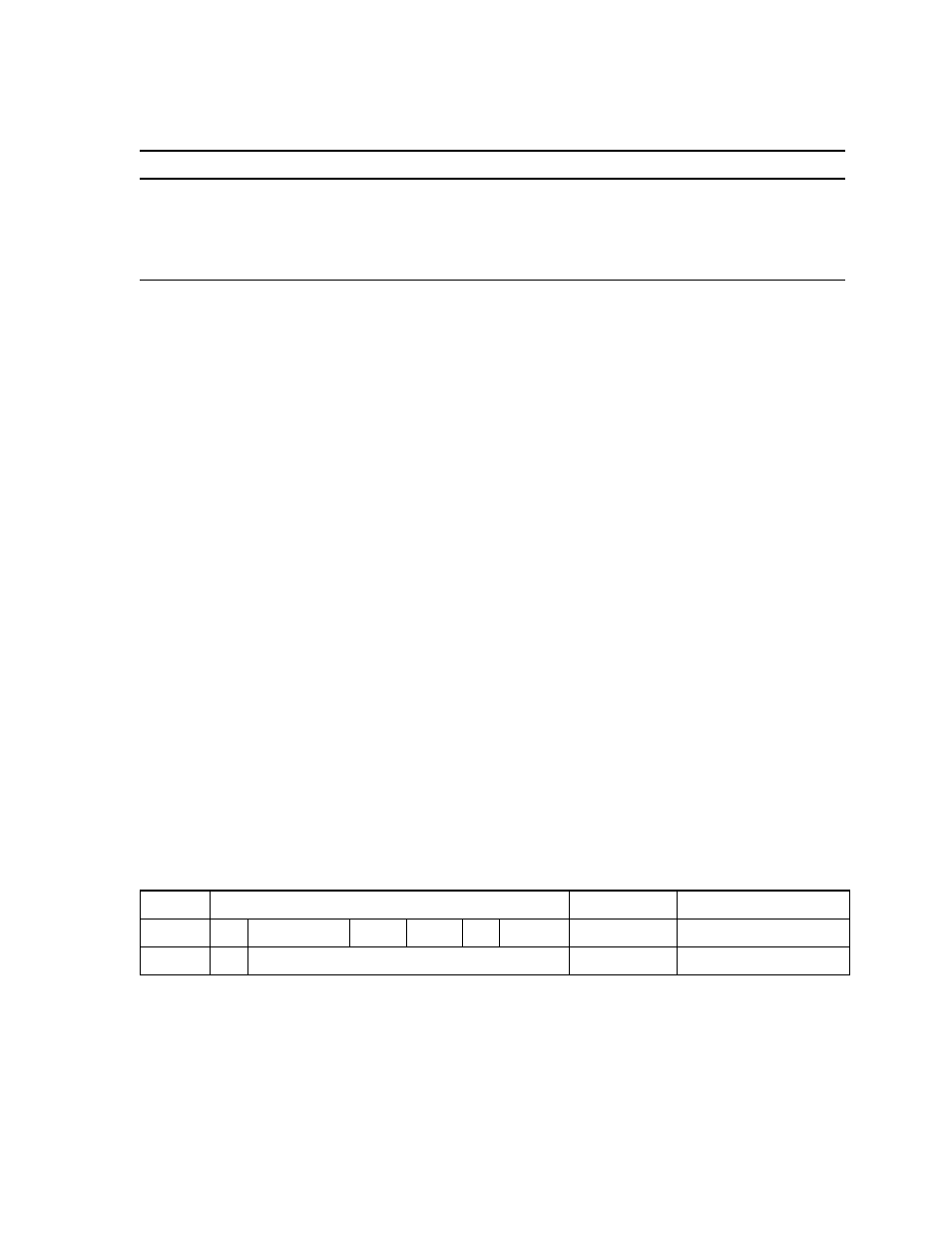

Table 4–23 Data Transfer Command Format

SysAddIn_L[14:2]

SysAddIn_L[1] SysAddIn_L[0]

Cycle 1

0

SysDc[4:0]

RVB

RPB

A

ID[3:0]

X

X

Cycle 2

C

X

X

X

Table 4–22 Next Cache Block State Selection by Probe[2:0] (Continued)

Probe[2:0]

Next Tag State