1 system port pins, System port pins, System interface signals – Compaq 21264 User Manual

Page 105: System port, 1 system port pins

Alpha 21264/EV67 Hardware Reference Manual

Cache and External Interfaces

4–17

System Port

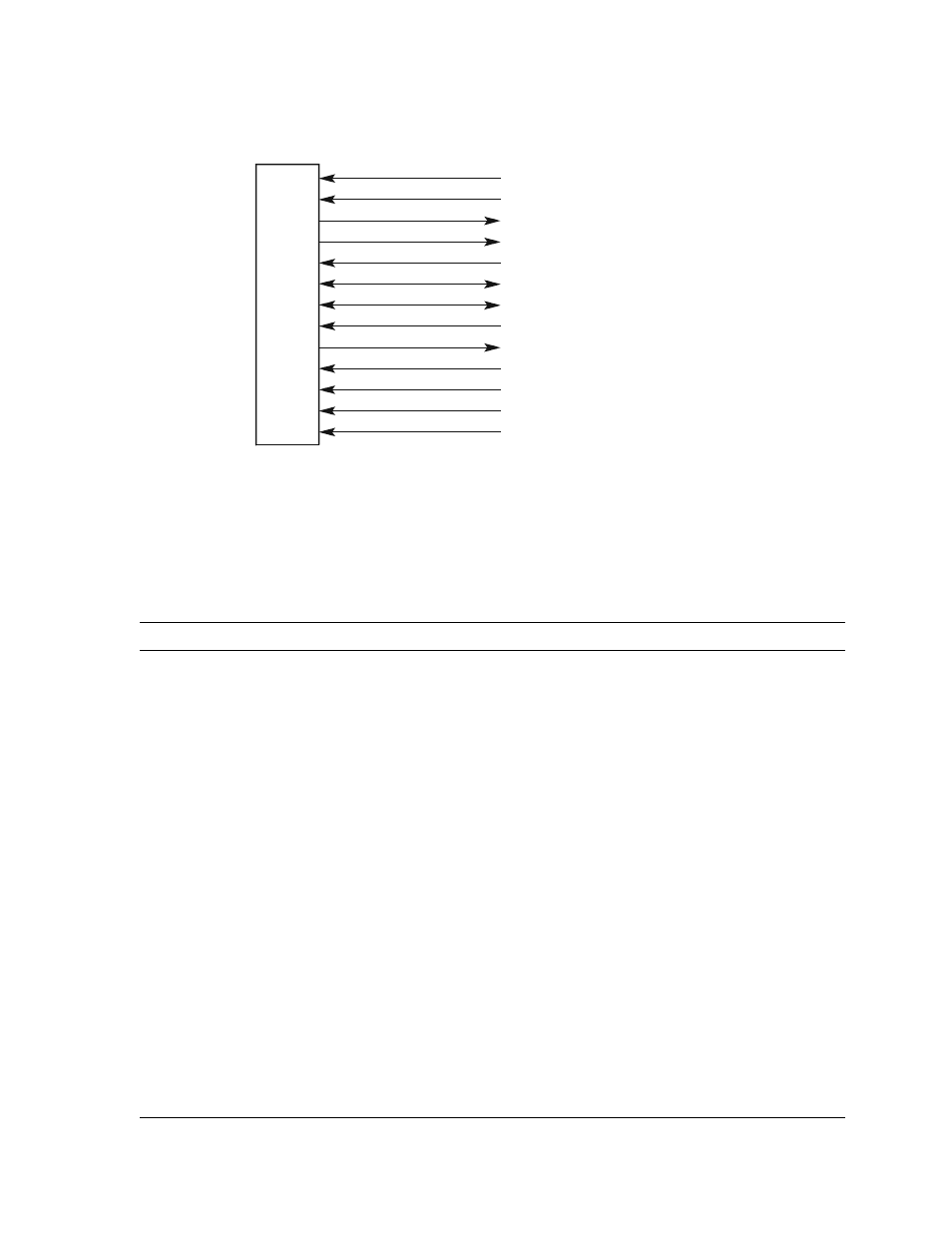

Figure 4–4 System Interface Signals

4.7.1 System Port Pins

Table 3–1 defines the 21264/EV67 signal types referred to in this section. Table 4–6

lists the system port pin groups along with their type, number, and functional descrip-

tion.

Table 4–6 System Port Pins

Pin Name

Type

Count Description

IRQ_H[5:0]

I_DA

6

These six interrupt signal lines may be asserted by the sys-

tem.

SysAddIn_L[14:0]

I_DA

15

Time-multiplexed SysAddIn, system-to-21264/EV67.

SysAddInClk_L

I_DA

1

Single-ended forwarded clock from system for

SysAddIn_L[14:0] and SysFillValid_L.

SysAddOut_L[14:0]

O_OD

15

Time-multiplexed SysAddOut, 21264/EV67-to-system.

SysAddOutClk_L

O_OD

1

Single-ended forwarded clock.

SysVref

I_DC_REF

1

System interface reference voltage.

SysCheck_L[7:0]

B_DA_OD

8

Quadword ECC check bits for SysData_L[63:0].

SysData_L[63:0]

B_DA_OD

64

Data bus for memory and I/O data.

SysDataInClk_H[7:0]

I_DA

8

Single-ended system-generated clocks for clock forwarded

input system data.

SysDataInValid_L

I_DA

1

When asserted, marks a valid data cycle for data transfers to

the 21264/EV67.

SysDataOutClk_L[7:0]

O_OD

8

Single-ended 21264/EV67-generated clocks for clock for-

warded output system data.

SysDataOutValid_L

I_DA

1

When asserted, marks a valid data cycle for data transfers

from the 21264/EV67.

SysFillValid_L

I_DA

1

Validation for fill given in previous SysDc command.

21264

SysAddIn_L[14:0]

FM-05652-EV67

SysAddInClk_L

SysAddOut_L[14:0]

SysAddOutClk_L

SysVref

SysData_L[63:0]

SysCheck_L[7:0]

SysDataInClk_H[7:0]

SysDataOutClk_L[7:0]

SysDataInValid_L

SysDataOutValid_L

SysFillValid_L

IRQ_H[5:0]