2 operation, Operation, Cmov decomposed –21 – Compaq 21264 User Manual

Page 205

Alpha 21264/EV67 Hardware Reference Manual

Privileged Architecture Library Code

6–21

Performance Counter Support

The CMOV instruction is decomposed into two valid fetched instructions that, in the

absence of stalls, are fetched in consecutive cycles. See Table 6–12 for more informa-

tion.

6.10.3.2 Operation

1. Setup

The following IPRs need to be set up by using PALcode instructions.

2. Open window

PCTR0 accumulates up to 4 valid fetched instructions per cycle when enabled via

I_CTL[PCT0_EN] and either I_CTL[SPCE] or PCTX[PPCE].

The valid fetched instruction that causes PCTR0 to overflow opens the window and

becomes the

p

rofiled instruction and covers a period of time near to when the

instruction was in flight. The first cycle of the window is the 5th cycle after the

instruction was fetched. A residual count of up to 7 valid fetched instructions is

accumulated in PCTR0 in the two cycles between overflow and the start of the Pro-

fileMe window. This residual count is returned in I_STAT[overcount(2,0)].

3. Count

If PCTR0 and PCTR1 are enabled, they increment according to modes selected by

SL0 & SL1.

4. End window

The last cycle of the window depends on whether the instruction traps, retires,

aborts, and/or is squashed by the fetcher.

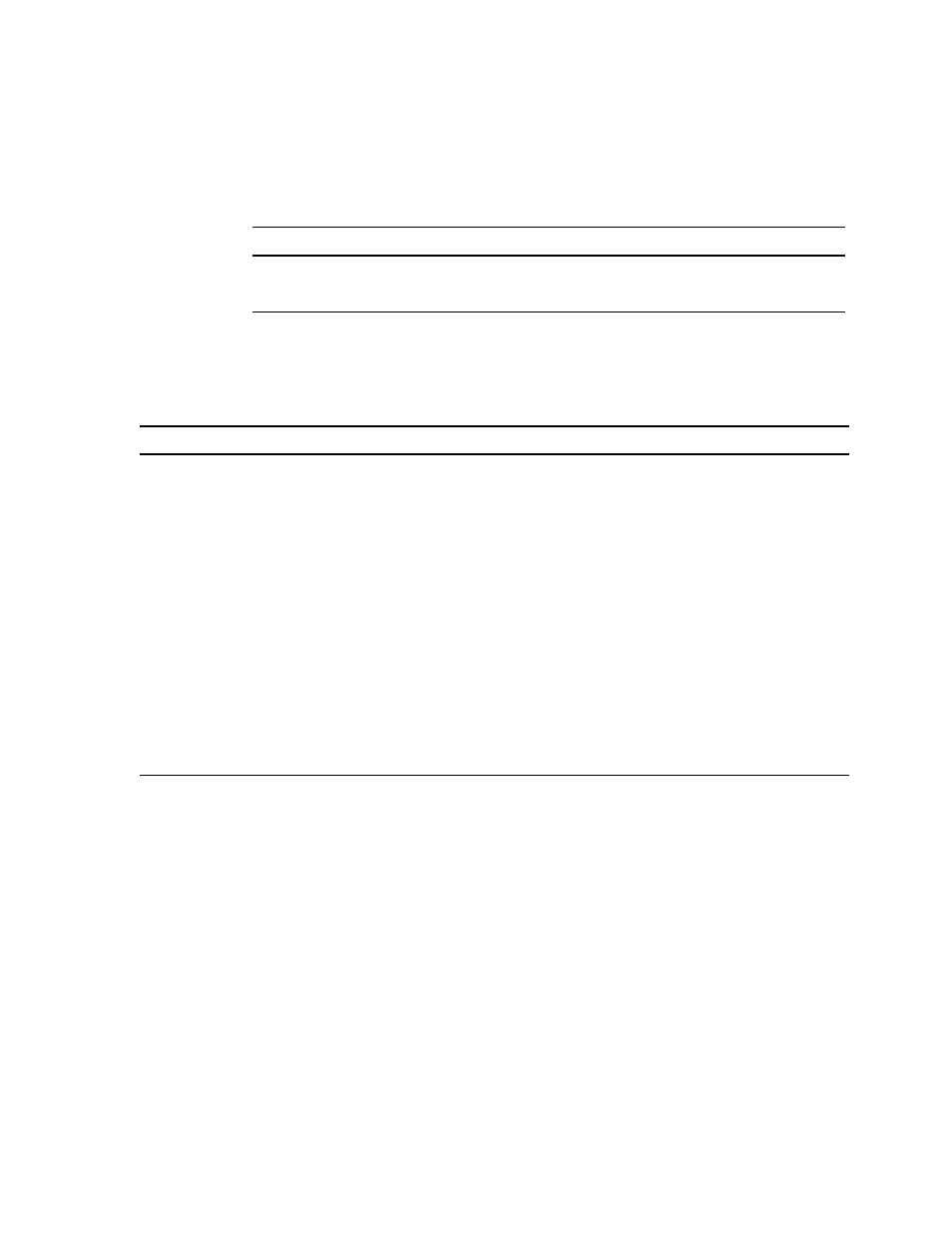

Table 6–12 CMOV Decomposed

Instruction

New Instructions

CMOV Ra, Rb--> Rc

CMOV1 Ra, oldRc

−−>

newRc1

CMOV2 newRc1, Rb

−−>

newRc2

IPR Name

Relevant Fields

Meaning

IER_CM

PCEN[1:0]

Enable Interrupts.

PCTX

PPCE

Enable Process Performance Counting or use I_CTL[SPCE].

PCTR_CTL

SL0

Selects Aggregate or ProfileMe mode; set to 1 for ProfileMe mode.

SL1

Selects PCTR0 and PCTR1 counting modes. See Table 6–14 for more infor-

mation.

PCTR0[19:0]

Set counter 0 value (2**20-N). This selects approximately the Nth valid

fetched instruction as the profiled instruction. Because writes to PCTR0 are

incremented by 0..4, the profiled instruction is one of the (N-4)th to Nth valid

fetched instructions. See Section 6.10.1 for more setup precautions.

PCTR1[19:0]

Set counter 1 value = 0. See Section 6.10.1 for more setup precautions.

I_CTL

SPCE

Enable System Performance Counting or use PCTX[PPCE].

PCT0_EN

Enable performance counter 0.

PCT1_EN

Enable performance counter 1.