3 hardware structure of implicitly written iprs, 4 ipr access ordering, Hardware structure of implicitly written iprs – Compaq 21264 User Manual

Page 193: Ipr access ordering, Paired instruction fetch order

Alpha 21264/EV67 Hardware Reference Manual

Privileged Architecture Library Code

6–9

Internal Processor Register Access Mechanisms

6.5.3 Hardware Structure of Implicitly Written IPRs

Implicitly written IPRs are physically built using only a single level of register, how-

ever the IPR has two hardware states associated with it:

1. Default State—The contents of the register may be written when an instruction gen-

erates an exception. If an exception occurs, write a new value into the IPR and go to

state 2.

2. Locked State—The contents of the register may only be overwritten by an except-

ing instruction that is older than the instruction associated with the contents of the

IPR. If such an exception occurs, overwrite the value of the IPR. When the trigger-

ing instruction, or instruction that is older than the triggering instruction, is killed

by the Ibox, go to state 1.

6.5.4 IPR Access Ordering

IPR access mechanisms must allow values to be passed through each IPR from a pro-

ducer to its intended consumers.

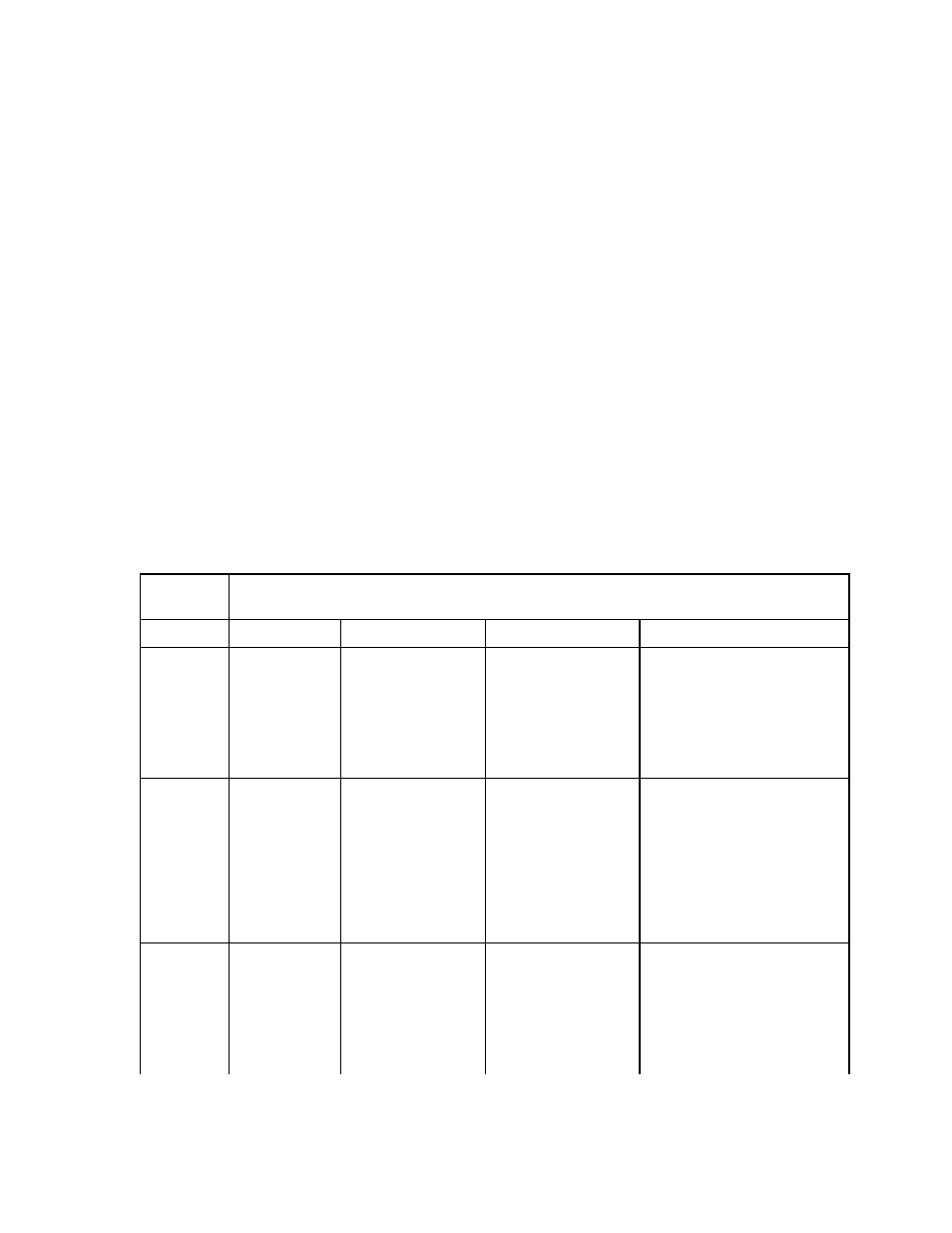

Table 6–7 lists all of the paired instruction orderings between instructions of the four

IPR access types. It specifies whether access order must be maintained, and if so, the

mechanisms used to ensure correct ordering.

Table 6–7 Paired Instruction Fetch Order

Second

Instruction

First Instruction

Implicit Reader

Implicit Writer

Explicit Reader

Explicit Writer

Implicit

Reader

Read transac-

tions can be

reordered.

No IPRs in this class. Read transactions can

be reordered.

A variety of mechanisms are

used to ensure order:

scoreboard bits to stall issue of

reader; HW_RET_STALL to

stall reader; double write plus

buffer blocks to force retire and

allow for propagation delay.

Implicit

Writer

No IPRs in this

class.

The hardware struc-

ture of implicitly

written IPRs handles

this case.

IPR-specific PALcode

restrictions are

required for this case.

An interlock mecha-

nism must be placed

between the explicit

reader and the implicit

writer (a read transac-

tion).

No IPRs in this class.

Explicit

Reader

Read transac-

tions can be

reordered.

If the reader is in the

PALcode routine

invoked by the

exception associated

with the writer, then

ordering is guaran-

teed.

Read transactions can

be reordered.

Scoreboard bits stall issue of

reader until writer is retired.