5 proberesponse commands (command[4:0] = 00001), Proberesponse commands (command[4:0] = 00001), Programming set_dirty_enable[2:0 – Compaq 21264 User Manual

Page 112: 21264/ev67 proberesponse command, E table 4–16 f

4–24

Cache and External Interfaces

Alpha 21264/EV67 Hardware Reference Manual

System Port

Systems that require an explicit indication of ChangeToDirty status changes initi-

ated by STx_C instructions can assert Cbox CSR STC_ENABLE[0]. When this

register field = 000, CleanToDirty and SharedToDirty commands are used. The dis-

tinction between a ChangeToDirty command generated by a STx_C instruction and

one generated by a STx instruction is important to systems that want to service

ChangeToDirty commands with dirty data from a source processor. In this case, the

distinction between a locked exclusive instruction and a normal instruction is criti-

cal to avoid livelock for a LDx_L/STx_C sequence.

4.7.5 ProbeResponse Commands (Command[4:0] = 00001)

The 21264/EV67 responds to system probes that did not miss with a 4-cycle transfer on

SysAddOut_L[14:0]. As shown in Table 4–14, the Command[4:0] field for a ProbeRe-

sponse command equals 00001. Table 4–17 shows the format of the 21264/EV67 Prob-

eResponse command.

Table 4–16 Programming SET_DIRTY_ENABLE[2:0]

SET_DIRTY_ENABLE

[2,0] (DS,CS,C)

Cbox Action

000

Everything acknowledged internally (uniprocessor).

001

Only clean blocks generate external acknowledge (CleanToDirty commands only).

010

Only clean/shared blocks generate external acknowledge (SharedToDirty command

only).

011

Clean and clean/shared blocks generate external acknowledge.

100

Only dirty/shared blocks generate external acknowledge (SharedToDirty commands

only).

101

Only dirty/shared and clean blocks generate external acknowledge.

110

Only dirty/shared and clean/shared blocks generate external acknowledge.

111

All transactions generate external acknowledge.

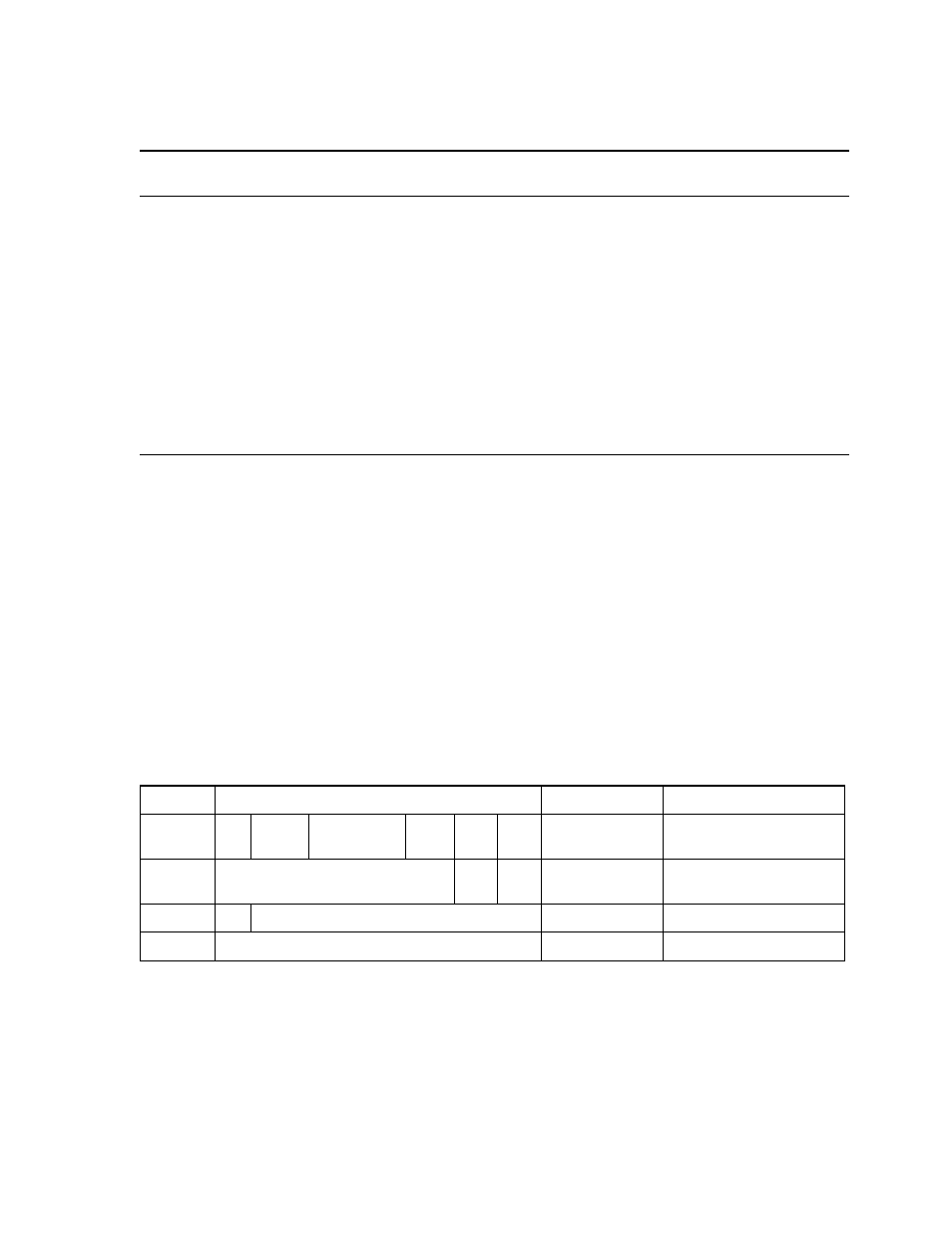

Table 4–17 21264/EV67 ProbeResponse Command

SysAddOut_L[14:2]

SysAddOut_L[1] SysAddOut_L[0]

Cycle 1

0

00001

Status[1:0]

DM

VS

VDB

[2:0]

X

X

Cycle 2

0

MS

MAF

[2:0]

X

X

Cycle 3

0

X

X

X

Cycle 4

X

X

X