4 hw_mfpr and hw_mtpr instructions, Hw_mfpr and hw_mtpr instructions, Hw_ret instruction format – Compaq 21264 User Manual

Page 190: Hw_mfpr and hw_mtpr instructions format, Hw_ret instruction fields descriptions, Opcodes reserved for palcode, 4 hw_mfpr and hw_mtpr instructions

6–6

Privileged Architecture Library Code

Alpha 21264/EV67 Hardware Reference Manual

Opcodes Reserved for PALcode

Figure 6–3 HW_RET Instruction Format

Table 6–5 describes the HW_RET instruction fields.

6.4.4 HW_MFPR and HW_MTPR Instructions

The HW_MFPR and HW_MTPR instructions are used to access internal processor reg-

isters. The HW_MFPR instruction reads the value from the specified IPR into the inte-

ger register specified by the RA field of the instruction. The HW_MTPR instruction

writes the value from the integer GPR, specified by the RB field of the instruction, into

the specified IPR. Figure 6–4 shows the HW_MFPR and HW_MTPR instructions for-

mat.

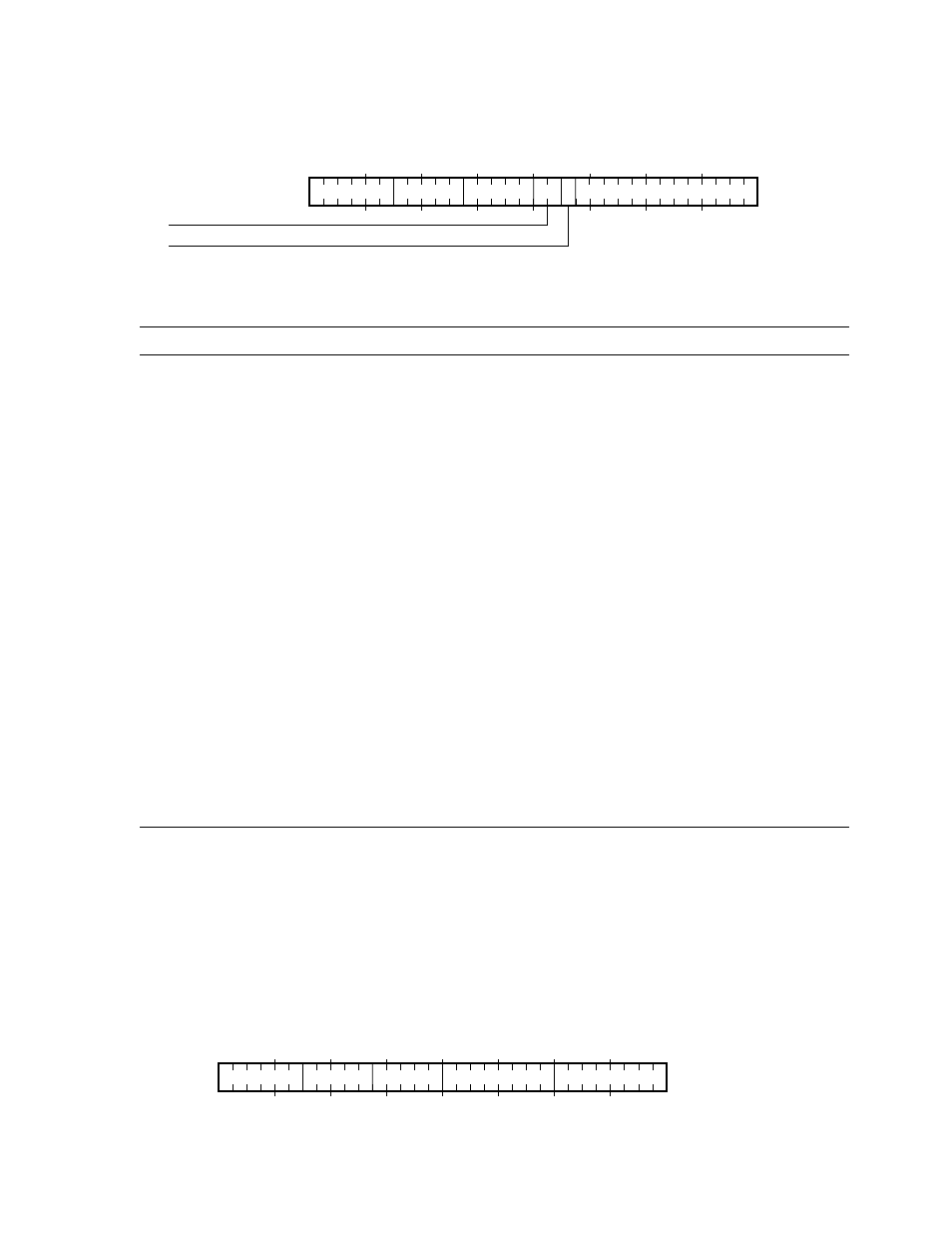

Figure 6–4 HW_MFPR and HW_MTPR Instructions Format

Table 6–5 HW_RET Instruction Fields Descriptions

Extent

Mnemonic Value

Description

[31:26]

OPCODE

1E

16

The opcode value.

[25:21]

RA

—

Register number. It should be R31.

[20:16]

RB

—

Target PC of the HW_RET instruction. Bit [0] of the register’s contents

determines the new value of PALmode.

[15:14]

HINT

00

01

10

11

HW_JMP — The PC is not pushed onto the prediction stack. The predicted

target is PC + (4*DISP[12:0]).

HW_JSR — The PC is pushed onto the prediction stack. The predicted

target is PC + (4*DISP[12:0]).

HW_RET — The prediction is popped off the stack and used as the target.

HW_COROUTINE — The prediction is popped off the stack and used as

the target. The PC is pushed onto the stack.

[13]

STALL

—

If set, the fetcher is stalled until the HW_RET instruction is retired or

aborted. The 21264/EV67 will:

•

Force a mispredict

•

Kill instructions that were fetched beyond the HW_RET instruction

•

Refetch the target of the HW_RET instruction

•

Stall until the HW_RET instruction is retired or aborted

If instructions beyond the HW_RET have been issued out of order, they

will be killed and refetched.

[12:0]

DISP

—

Holds a 13-bit signed longword displacement.

31

26 25

21 20

16 15

13 12

0

FM-05656.AI4

HINT

STALL

14

DISP

RB

RA

OPCODE

31

26 25

21 20

16 15

0

FM-05657.AI4

8

7

SCBD_MASK

RB

RA

OPCODE

INDEX