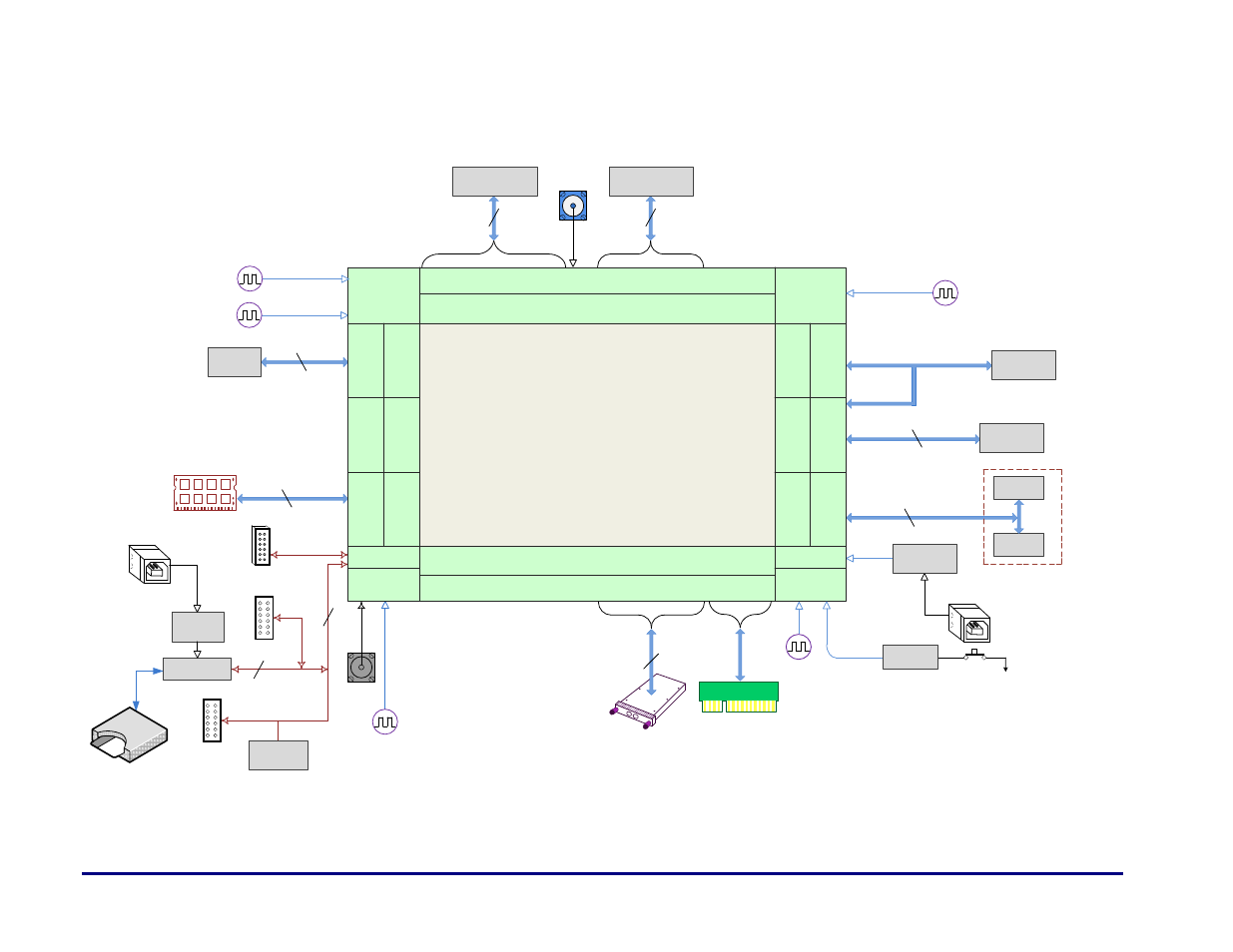

Figure 9: hd1000 fpga interfaces, Hd1000 fpga interfaces, Hd1000 fpga top view – Achronix Speedster22i HD1000 Development Kit User Guide User Manual

Page 26: Pll serdes - top serdes - bottom

26

UG034, July 1, 2014

HD1000 FPGA Interfaces

BLN

BLN

BLN

CNFG

B

A

N

K

E

A

S

T

-C

E

N

T

R

E

(B

Y

T

E

0

-1

2

)

B

A

N

K

E

A

S

T

-N

O

R

T

H

(B

Y

T

E

0

-1

2

)

B

A

N

K

E

A

S

T

-S

O

U

T

H

(B

Y

T

E

0

-1

2

)

BLN

BLN

BLN

B

A

N

K

W

E

S

T

-C

E

N

T

R

E

(B

Y

T

E

0

-1

2

)

B

A

N

K

W

E

S

T

-N

O

R

T

H

(B

Y

T

E

0

-1

2

)

B

A

N

K

W

E

S

T

-S

O

U

T

H

(B

Y

T

E

0

-1

2

)

WEST-NORTH

PLL

SERDES - TOP

SERDES - BOTTOM

GPIO

EAST-NORTH

PLL

EAST-SOUTH

PLL

HD1000 FPGA

TOP VIEW

WEST-SOUTH

PLL

SFLASH

64Mbit

ATMEL MICRO

256KB 8MHZ

FTDI CHIP

FT232RL

QDR II +

2MbX36

FMC

CONNECTOR

2Gb DISCRETE

DDR3 1x16 BIT

RLDRAM-3

16MbX36

RLDRAM-3

16MbX36

8

SD CARD

HEADER

SMA

CLK OSCILLATOR

PCI EXPRESS LLC

(X8)

16

72

Width

Expansion

USB 2.0 B

JTAG HEADER

JTAG

204 - SO-DIMM

X64

USB 2.0 B

SPI

SMA

36

64

x8

SYNTHESIZER CLK

12

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

CFP

10

10

U22

U33

J1/J2

J41

J11

U41

U35

J14

J35

U54

U31/U36

U21

J3

FTDI CHIP

FT232RL

FMC-Serdes Group

INTERLAKEN

HEADER

J20

J28

FMC CLK

RESET1

SYNTHESIZER CLK

S1

FMC CLK

Figure 9: HD1000 FPGA Interfaces