Rockwell Automation 1785-Vx0B, D17856.5.9 PLC-5 VME VMEbus Programmable Controllers User Manual User Manual

Page 43

Chapter 3

VMEbus Interface

3-5

Unless otherwise noted, register bits:

are initialized to 0 at reset.

directly control the associated hardware function, so that changing a

register bit has an instantaneous effect on the function it controls.

The ID register, whose value is CFEC (hex), and the next (device-type)

register, 7FE8(hex), uniquely identify the PLC-5/VME processor.

The status/control register contains status and control bits, primarily for

use by a separate VME CPU (see Table 3.A).

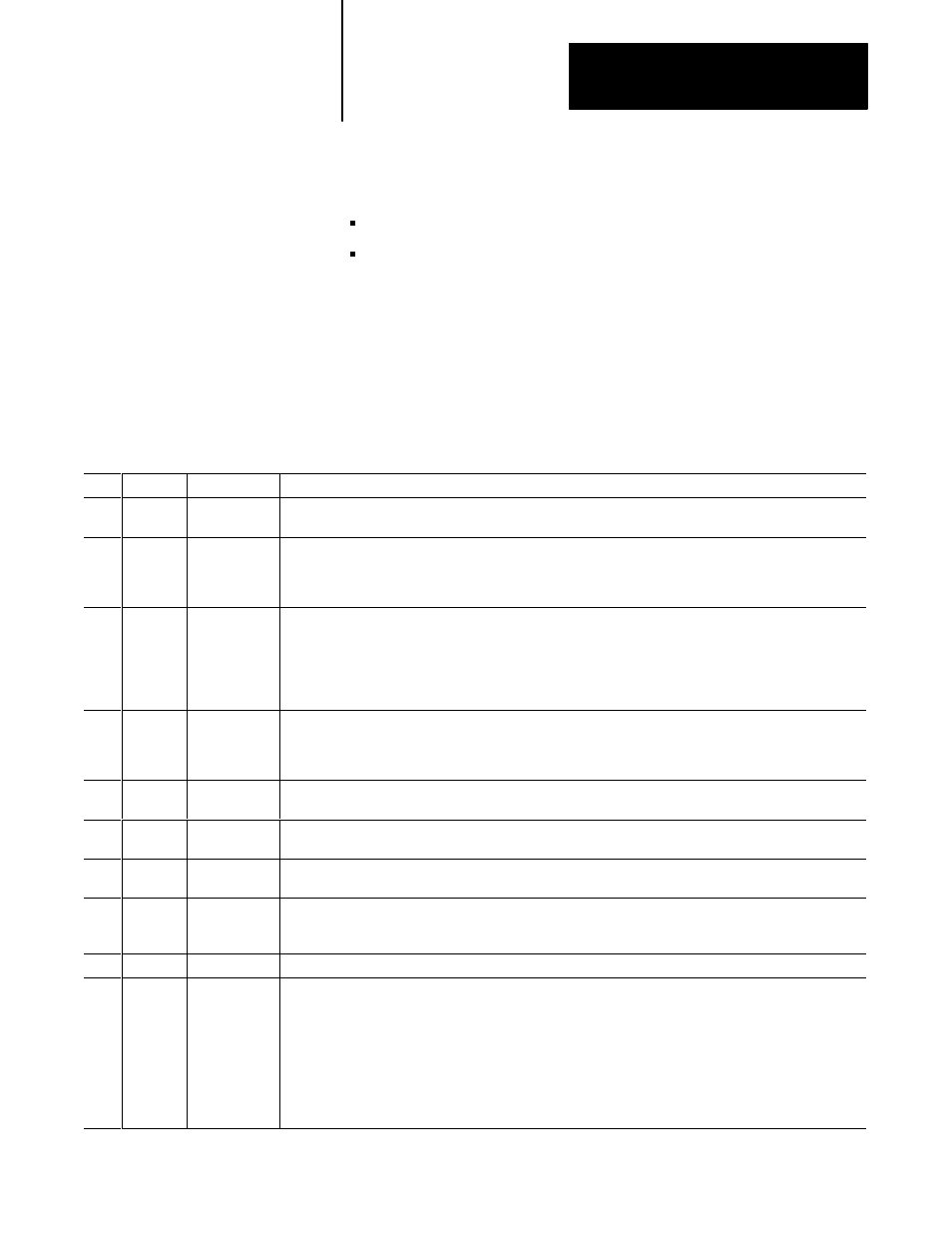

Table 3.A

Status/Control Register

Bit

Register

Function

Definition

15

GRE

Global RAM

enable

If set by an application program (1), the PLC-5/VME processor is enabled as an VMEbus A24 slave. This bit is

not altered by the PLC-5/VME firmware. The 64K of global RAM is enabled by this bit.

12

SYSF

SYSFAIL

The PLC-5/VME processor drives the VME SYSFAIL line and the SYSFAIL LED on the front panel while this bit

is 0. This bit is set (to 1) by the PLC-5/VME processor firmware at initialization and not altered thereafter by the

PLC-5/VME processor unless a hardware failure occurs. One purpose of this bit is to allow a separate VMEbus

CPU to determine which VME module is asserting SYSFAIL.

10

NOCV

No check VME

status file

The VME status file, a file in the PLC-5/VME processor memory holds certain state information for compatibility

with the 6008-LTV processor. As in the 6008-LTV processor, ladder programs can modify certain parts of the

VME status file. If NOCV is 0, the PLC-5/VME processor checks its VME status file every scan loop to see if any

parameters have changed. This will increase your processor scan and communication time. You should

initialize this bit to 0 if you are changing the status file from a ladder program or if you are using 6200 software

from an external device. See Chapter 7 for more information.

7

SRIE

SYSRESET

input enable

If 1, VME SYSRESET causes a full hardware reset of the PLC-5/VME processor. If reset, VME SYSRESET is

ignored by the processor, except for resetting its VMEbus interface and terminating any current VMEbus

operations. This bit is reset by a hardware reset and set by PLC-5/VME processor firmware early in its

initialization process.

6

RELM

Bus release

mode

If 1, the bus release mode is ROR, otherwise it is RWD. This bit is not altered by the PLC-5/VME processor.

Bus release mode only applies to PLC-5/VME processor that behaves as a VMEbus master.

5

MYAS

My address

strobe

When 0, the PLC-5/VME processor is in the midst of VMEbus master transfer. This state bit is not intended for

use by other masters; it has meaning to only the PLC-5/VME processor’s firmware.

3

RDY

Ready

If 1, the PLC-5/VME processor is ready to accept commands. RDY and PASS are alerted at the same point by

the PLC-5/VME processor.

2

PASS

Self-test

passed

This bit is set by the PLC-5/VME processor after initialization if its self-test completes successfully. The bit is not

altered thereafter by the PLC-5/VME processor. If RDY=1 and PASS=0, the PLC-5/VME processor has failed its

self-test.

1

NOSF

SYSFAIL inhibit

If 1, the PLC-5/VME processor cannot assert SYSFAIL. This bit is not altered by the PLC-5/VME processor

0

RSTP

Reset

If 1, the PLC-5/VME processor is in the reset state. During the reset state, the PLC-5/VME processor is inactive

and pending interrupts and bus requests are cleared. This register set is active and can be accessed by other

VMEbus devices. This bit is not altered by the PLC-5/VME firmware.

Changing it from 1 to 0 releases the PLC from its reset state and it follows its normal power sequence (if the

PLC-5/VME processor is not in a faulted state).

Attention: This bit causes the processor to reset and the I/O to stop communicating. Unpredictable operation

may occur with possible damage to equipment and/or injury to personnel.