Rainbow Electronics AT76C551 User Manual

Page 61

61

AT76C551

1612D–08/01

Note:

Default: 00h

Bit 2

W

RX Setup

The USB hardware sets this bit when it

receives a valid setup packet from the

Host. This bit is used by Control Endpoints

only.

This bit is used only by Control Endpoints to signal

the processor that the USB hardware has received a

valid SETUP packet, and that the data portion of the

packet is stored in the FIFO. The hardware will clear

all other bits in this register and will set RX SETUP. If

the corresponding interrupt is enabled, the processor

will be interrupted when RX SETUP is set. After the

data has been completely read from the FIFO the

firmware should clear this bit.

Bit 1

W

RX OUT Packet

Indicates that the USB hardware has

decoded an OUT token and that the data

is in the FIFO.

The USB hardware sets this bit after it has stored the

data of an OUT transaction in the FIFO. While this bit

is set, the hardware will NAK all OUT tokens. For

Control Endpoints only, bit 7 of this register, Enable

Control Write, has to be set for the hardware to

accept the OUT data. The USB hardware will not

overwrite the data in the FIFO except for an early

USB Setup Request. Bit RX OUT Packet is used for

the following operations:

Control write transactions by a Control Endpoint

OUT transaction with DATA1 PID to complete the

status phase of a control Endpoint.

By a BULK OUT or ISO OUT or INT OUT

Endpoint

Setting this bit causes an interrupt to the processor if

the interrupt is enabled. The firmware clears this bit

after the FIFO are read.

Bit 0

R

TX Complete

The hardware sets this bit to indicate to a

Control Endpoint that it has received an

ACK handshake from the Host.

This bit is used by hardware in a Control Endpoint to

signal to the processor that it has successfully

completed certain transactions. TX Complete is set at

the completion of a:

Control read data stage

Status stage without data stage

Status stage after a control write transaction

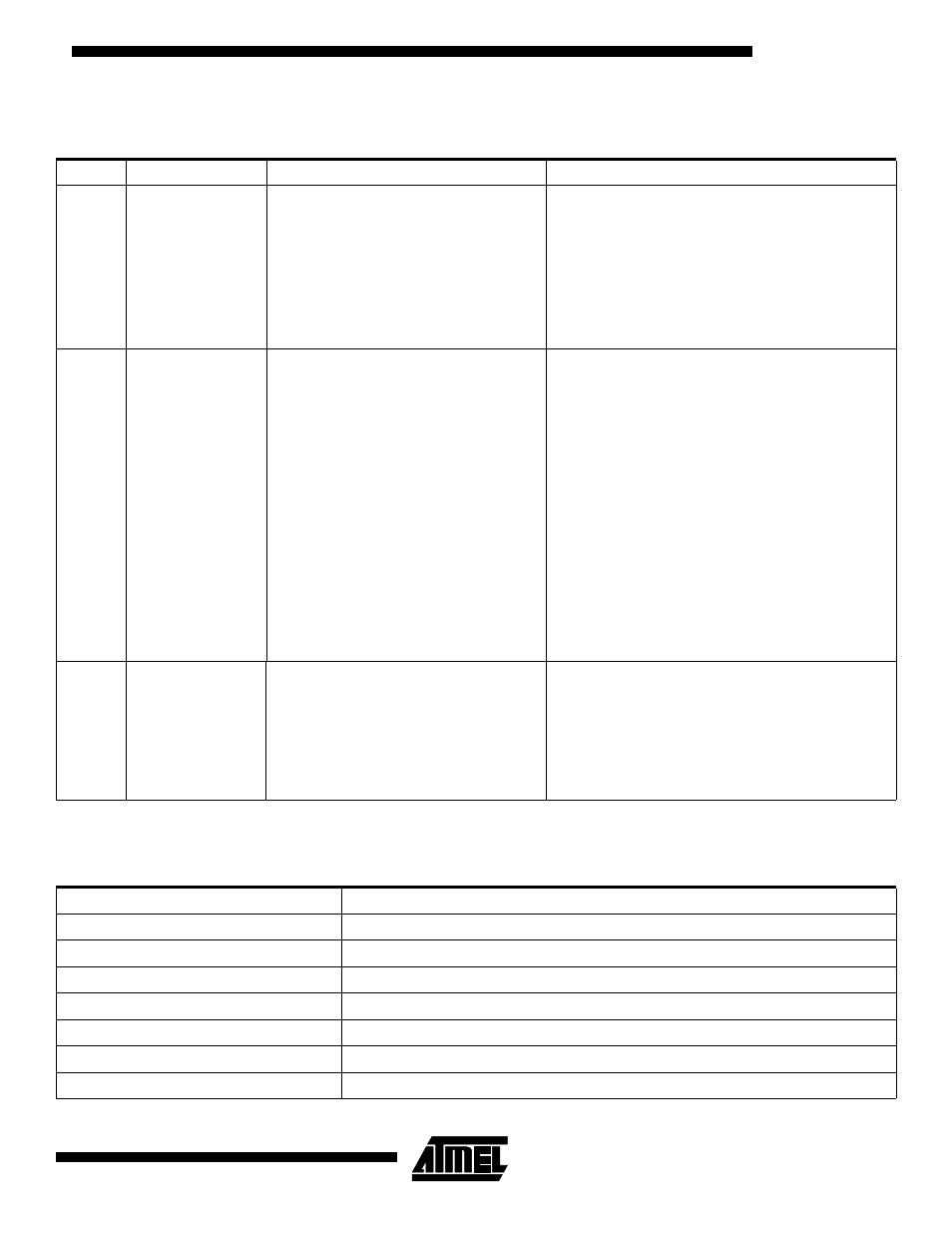

Table 8. Endpoint Control and Status Register (Continued)

addr: see below

8 bits

Bit

Bit Name

Function

Description of Bit

Table 9. Endpoint Control and Status Register’s Address

Address

Register

D00037Ch

FCSR0 Endpoint 0

D000378h

FCSR1 Endpoint 1

D000374h

FCSR2 Endpoint 2

D000370h

FCSR3 Endpoint 3

D00036Ch

FCSR4 Endpoint 4

D000368h

FCSR5 Endpoint 5

D000364h

FCSR6 Endpoint 6