Rainbow Electronics AT76C551 User Manual

Page 60

60

AT76C551

1612D–08/01

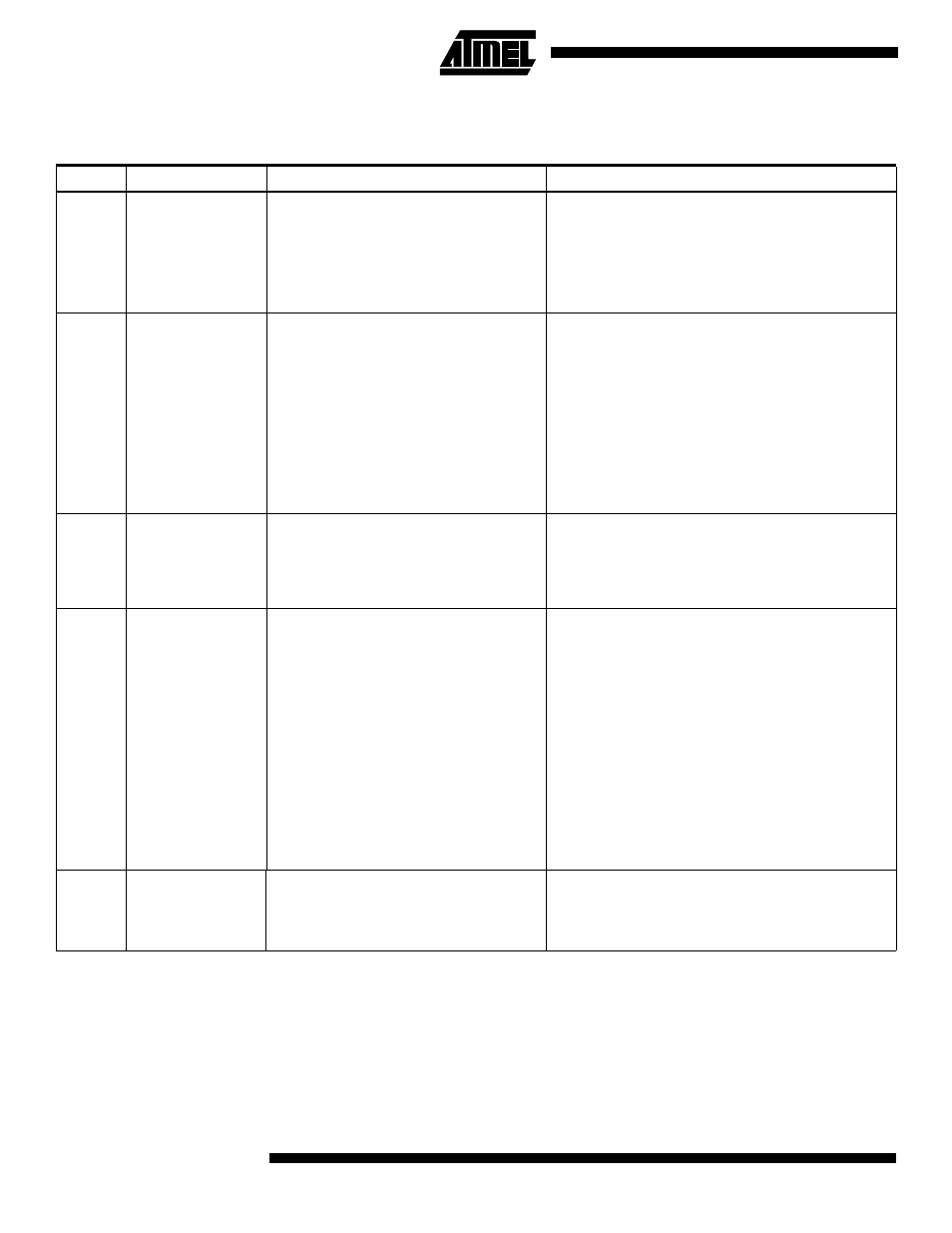

Table 8. Endpoint Control and Status Register

addr: see below

8 bits

Bit

Bit Name

Function

Description of Bit

Bit 7

R

Control Direction

Set by the processor to indicate to the

USB hardware the direction of a control

transfer.

0 = control write. No data stage

1 = control read

This bit is used by Control Endpoints only.

This bit is only used by Control Endpoints. It is used

by firmware to indicate the direction of a control

transfer. It is written by the firmware after it receives a

RX SETUP interrupt. The hardware uses this bit to

determine the status phase of a control transfer.

Bit 6

R

Data End

Indicates that the processor has placed

the last data packet in FIFO0, or that the

processor has processed the last data

packet it expects from the Host.

This bit is used only by Control Endpoints. Together

with bit 1 (TX Packet Ready) it will signal the USB

hardware to go to the STATUS phase after the packet

currently residing in the FIFO is transmitted.

After the hardware completes the STATUS phase it

will interrupt the processor without clearing this bit.

CAUTION: Since the Data End bit signals “END OF

TRANSACTION” any other Endpoint controller bit set

after the DATA END is not considered by the Ping-

pong controller. For this reason, Tx_Packet Ready

should be set before Data_End.

Bit 5

R

Force Stall

Set by the processor to indicate a stalled

Endpoint. The hardware will send a

STALL handshake as a response to the

next IN or OUT token.

The processor sets this bit if it wants to force a STALL

after an unsupported request is received, or if the

Host continues to ask for data after the data is

exhausted. This bit should be set at the end of any

data phase or setup phase.

Bit 5

R/C

TX Packet Ready

Indicates that the processor has loaded

the FIFO with a packet of data. This bit is

cleared by hardware after the USB Host

acknowledges the packet. For ISO

Endpoints, this bit is cleared

unconditionally after the data is sent.

This bit is used for the following operations:

Control read transactions by a Control Endpoint.

IN transactions with DATA1 PID to complete the

status phase for a Control Endpoint, when this bit

is "0”, but bit Data End (bit 4) is "1”.

By a BULK IN or ISO IN or INT IN Endpoint.

The processor should write to the FIFO only if this bit

is cleared. The bit will be set after it has completed

writing the data. The data can be a zero length. For a

Control Endpoint the processor should write to the

FIFO only while bit 6 (TX Packet Requested) is set.

The hardware clears this bit after it receives an ACK.

If the interrupt is enabled, clearing this bit by the

hardware, it causes an interrupt to the processor.

Bit 3

W

Stall Snd

The USB hardware sets this bit after a

STALL is sent to the Host.

Indicates End of data stage for the Control

Endpoint only.

The USB hardware sets this bit after a STALL has

been sent. The firmware uses this bit when

responding to a USB GetStatus Request.