4 address areas of system memory – Siemens Simatic S7-300 CPU 31xC and CPU 31x S7-300 User Manual

Page 67

Memory concept

4.1 Memory areas and retentivity

CPU 31xC and CPU 31x, Technical data

Manual, Edition 08/2004, A5E00105475-05

4-5

4.1.4

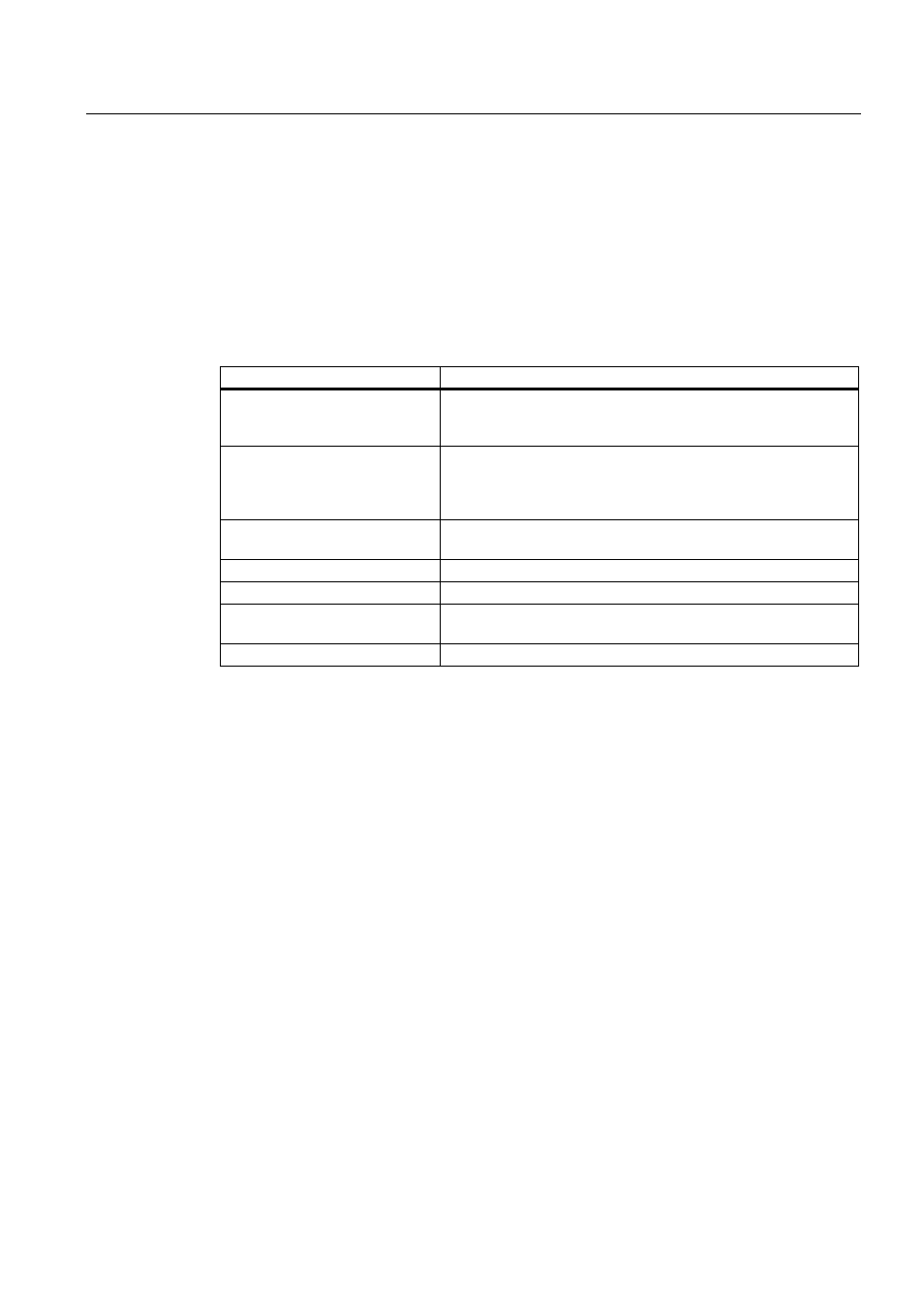

Address areas of system memory

System memory of the S7 CPUS is organized in address areas (refer to the table below). In

a corresponding operation of your user program, you address data directly in the relevant

address area.

Address areas of system memory

Table 4-4

Address areas of system memory

Address areas

Description

Process image of inputs

At every start of an OB1 cycle, the CPU reads the values at the

input of the input modules and saves them the process image of

inputs.

Process image of outputs

During its cycle, the program calculates the values for the outputs

and writes these to the process image of outputs. At the end of

the OB1 cycle, the CPU writes the calculated output values to the

output modules.

Flag bits

This area provides memory for saving the intermediate results of

a program calculation.

Timers

Timers are available in this area.

Counters

Counters are available in this area.

Local data

Temporary data in a code block (OB, FB, FC) is saved to this

memory area while the block is being edited.

Data blocks

See

Recipes and measurement value logs

Reference

The address areas of your CPU are listed in the

Instruction list for CPUs 31xC and 31x.

I/O process image

When the user program addresses the input (I) and output (O) address areas, it does not

query the signal states of digital signal modules. Instead, it rather accesses a memory area

in CPU system memory. This particular memory area is the process image.

The process image is organized in two sections: The process image of inputs, and the

process image of outputs.

Advantages of the process image

Process image access, compared to direct I/O access, offers the advantage that a consistent

image of process signals is made available to the CPU during cyclic program execution.

When the signal status at an input module changes during program execution, the signal

status in the process image is maintained until the image is updated in the next cycle.

Moreover, since the process image is stored in CPU system memory, access is significantly

faster than direct access to the signal modules.