3 retentivity of memory objects – Siemens Simatic S7-300 CPU 31xC and CPU 31x S7-300 User Manual

Page 65

Memory concept

4.1 Memory areas and retentivity

CPU 31xC and CPU 31x, Technical data

Manual, Edition 08/2004, A5E00105475-05

4-3

Retentive data in RAM

Therefore, the contents of retentive DBs are always retentive at restart and POWER

ON/OFF.

CPUs V2.1.0 or higher also support volatile DBs (the volatile DBs are initialized at restart of

POWER OFF-ON with their initial values from load memory.)

See also

Properties of the Micro Memory Card (MMC) (Page 4-9)

4.1.3

Retentivity of memory objects

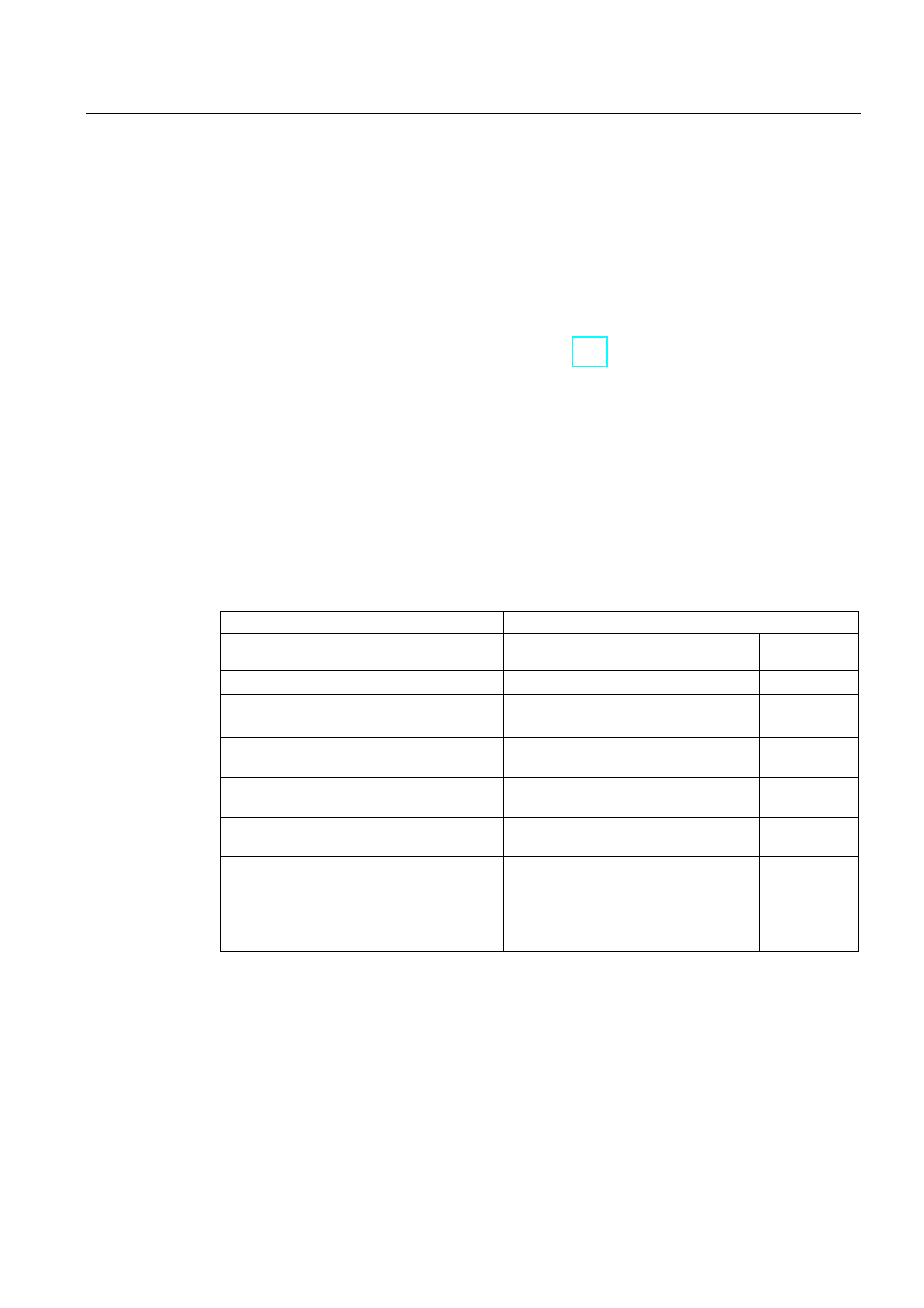

Retentive behavior of memory objects

The table below shows the retentive behavior of memory objects during specific operating

state transitions.

Table 4-2

Retentive behavior of memory objects (applies to all CPUs with DP/MPI-SS

(31x-2 PN/DP)

Memory object

Operating state transition

POWER ON /

POWER OFF

STOP →

RUN

CPU memory

reset

User program/data (load memory)

X

X

X

•

Retentive behavior of DBs for CPUs

with firmware < V2.1.0

X

X

–

•

Retentive behavior of DBs for CPUs

with firmware >= V2.1.0

Can be set in the properties of the DBs

in STEP 7 V5.2 + SP1 or higher.

–

Flag bits, timers and counters configured as

retentive data

X

X

–

Diagnostics buffers, operating hour

counters

X

X

X

MPI address, transmission rate

(or also DP address, transmission rate of

the MPI/DP interface of CPU 315-2 PN/DP

and CPU 317, if these are configured as

DP nodes.)

X

X

X

x = retentive; – = not retentive

Retentive behavior of a DB for CPUs with firmware < V2.1.0

For these CPUs, the contents of the DBs are always retentive at POWER ON/OFF or STOP-

RUN.