2 i/o address map, I/o address map -5 – Intel 460GX User Manual

Page 85

Intel® 460GX Chipset Software Developer’s Manual

4-5

System Address Map

4.2

I/O Address Map

The 460GX chipset allows I/O addresses to be mapped to resources supported on the I/O buses

underneath the 460GX chipset controller. This I/O space is partitioned into sixteen 4K byte

segments. Each of the segments can be individually configured to any I/O bus. Segment 0 is always

assigned to the compatibility I/O bus (of which there is only one per system).

There are four classes of I/O addresses that are specifically decoded by the 460GX chipset:

•

All I/O addresses less than 100h: These addresses are specifically decoded as “defer-only”

addresses. The SAC does not post any I/O accesses to this range, regardless of the state of the

I/O posting enable bit. This is necessary because I/O accesses below 100h have historically

had ordering side effects: e.g. accesses to the 8259 Interrupt Masks.

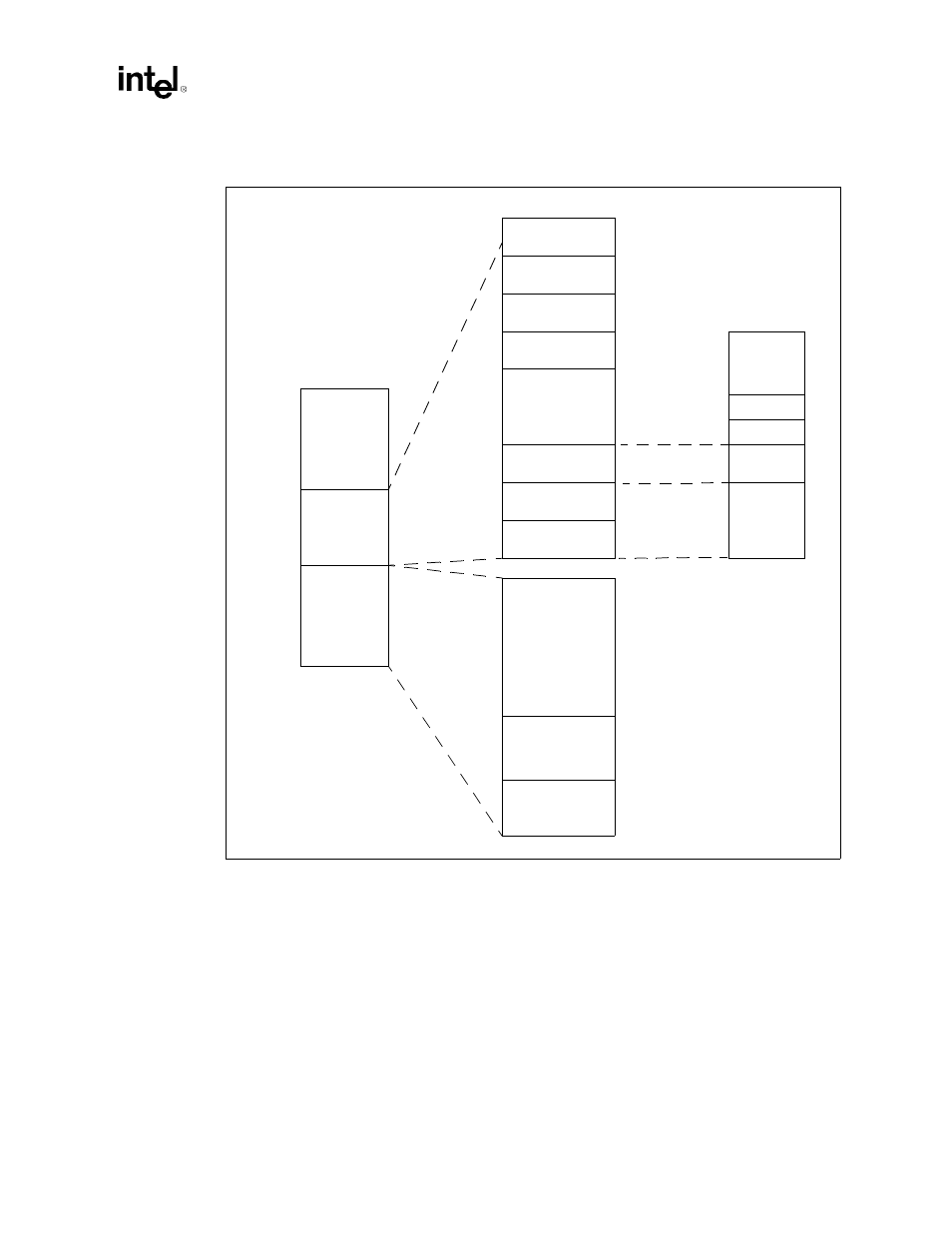

Figure 4-2. Itanium™ Processor and Chipset-specific Memory Space

System

16 MB

FEC0_0000

FF00_0000

FE00_0000

12 MB

Chipset

4 MB

Specific

FFFF_FFFF

Chipset

Reserved

8 MB

I/O reserved

I/O SAPIC #0

I/O SAPIC #1

I/O SAPIC #2

I/O SAPIC #255

FEC0_0000

FEC0_1000

FEC0_2000

FECF_F000

FED0_0000

I/O SAPIC

#3 to # 254

FEFF_FFFF

2 MB

GART Table

2 MB

FEBF_FFFF

FE40_0000

FE20_0000

FE00_0000

FE60_0000

4KB each

FEC0_3000

PCI Bus 0A

PCI Bus 0B

PCI Bus 1A

PCI Bus 2A

PCI Bus mapping

of SAPIC addresses.

I/O reserved

Interrupt Delivery

On system bus - 1MB

1 MB

1 MB

FEF0_0000

FEE0_0000

Chipset

Reserved

Processor

Specific

Firmware