2 power management 1 enable, 3 power management 1 control – Intel 460GX User Manual

Page 222

LPC/FWH Interface Configuration

11-32

Intel® 460GX Chipset Software Developer’s Manual

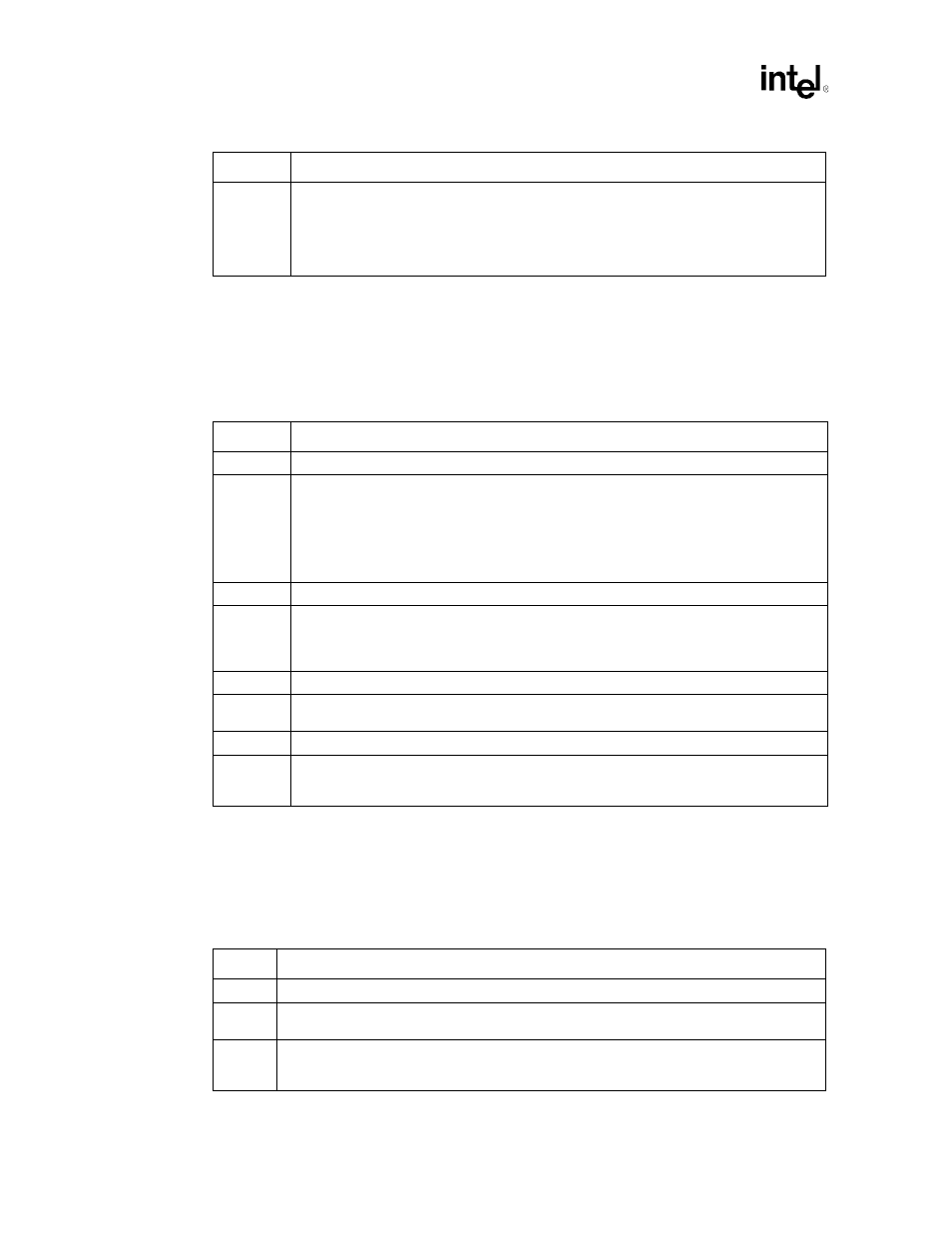

11.2.7.2

Power Management 1 Enable

Address Offset:

02-03h

Attributes:

Read/Write

Default Value:

Bit 10: Undefined, All other bits ‘0’

Size:

16 bits

11.2.7.3

Power Management 1 Control

Address Offset:

04-05h

Type:

Read/Write

Default Value:

Bits 12:10 Undefined, All other bits ‘0’

Size:

16 bits

0

TMROF_STS: This is the timer overflow status bit. This bit gets set anytime the 22

nd

bit of the

24 bit timer goes from high to low (bits are counted from 0 to 23). This will occur every 2.3435

seconds. When the TMROF_EN bit is set, the setting of the TMROF_STS bit will generate an

SCI or SMI. SMI will be generated if ACPI_TMR_EN, SMI_EN and TMROF_EN are set, and

SCI_EN is not set. SCI will be generated if SCI_EN and TMROF_EN are set. The SCI or SMI

handler clears this bit by writing a 1 to it.

Bit

Description

Bit

Description

15:11

Reserved.

10

RTC_EN: This bit is used to enable the setting of the RTC_STS bit to generate a wake event.

The RTC_STS bit is set anytime the RTC generates an alarm (asserts the IRQ8# signal active).

The enable bit does not have to be set to enable the setting of the RTC_STS bit by the assertion

of the RTC alarm. The value of this bit must be maintained, even through a G3 state. The IFB

will not resume, from RTC, after power failure (RSMRST# low) even if this bit is set. This bit is

automatically cleared by a power button override. The IFB can resume from RTC if only

PWROK goes low with RSMRST# high. Upon reset, this bit is undefined.

9

Reserved.

8

PWRBTN_EN: This bit is set to 1 to enable the setting of the PWRBTN_STS bit to also

generate an SCI or SMI. Even if the PWRBTN_EN bit is set to 0, the power button can always

generate a Wake event (if in a n S1-S5 state), and the power button override can cause an

unconditional transition to the S5 state.

7:6

Reserved.

5

GBL_EN: Global enable bit. When both GBL_EN and GBL_STS are set, an SCI event is

generated.

4:1

Reserved.

0

TMROF_EN: This is the timer overflow interrupt enable bit. When this bit is set then an SCI or

SMI is generated anytime the TMOF_STS bit is also set. When this bit is reset, then no interrupt

is generated when the TMROF_STS bit is set.

Bit

Description

15:14

Reserved.

13

SLP_EN: This is a write-only bit and reads to it always return a zero. Setting this bit causes the

system to sequence into the Sleep state defined by the SLP_TYP field.

12:10

SLP_TYP: This 3-bit field defines the type of Sleep the system should enter when the SLP_EN bit

is set to 1. IFB doesn’t directly support any modes other than those listed in this table. Other Sleep

states can be supported in external logic.