11 pci integrity, 1 pci bus monitoring, 2 pxb as master – Intel 460GX User Manual

Page 118

Data Integrity and Error Handling

6-20

Intel® 460GX Chipset Software Developer’s Manual

6.11

PCI Integrity

The PCI bus provides a single even-parity bit

(PAR)

that covers the

AD[31:0]

and

C/BE#[3:0]

lines. The agent that drives the

AD[31:0]

lines is responsible for driving

PAR

. Any undefined

signals must still be driven to a valid logic level and included in the parity calculation.

6.11.1

PCI Bus Monitoring

When the PXB is not the PCI bus master, it will still check the address parity for all PCI address

phases. If a parity error is detected and the Parity Error Response is enabled in the PCI Command

(

PCICMD

) register, the event is logged in the Parity Error Detected bit in the PCI Status

(

PCISTS

) register. If the

PCICMD

register’s

SERR#

Enable bit (

SERRE

) is set, SERR# will

also be asserted. When the PXB asserts

SERR#

, the

PCISTS

register’s Signalled System Error bit

(

SSE

) is also set.

Note that the expected settings for the GX system are: SERRE=1, PERRE=1, ERRCMD[3]=1, and

ERRCMD[4]=1. ERRCMD[6:5] are to be programmed as each OEM, operating system or system

user desires in order to enable SERR reporting of data parity errors. For data which has bad parity

and is received from the PCI bus, the PXB will forward this up the Expander bus as if there were no

parity error, so that ERRCMD[5] may need to be set for sufficient error containment, since PERR#

asserted to the card will not prevent the data which had a parity error from being placed in memory

6.11.2

PXB as Master

6.11.2.1

Master Abort

If the PXB initiates a PCI transaction and no target responds, the PXB will terminate the

transaction with a master-abort. The PXB will wait five PCI clocks after asserting

FRAME#

for a

target to respond with

DEVSEL#

. If no target responds, the PXB will perform a master abort to

terminate the cycle on the PCI bus. Special Cycle commands, which are broadcast to all PCI

targets, will always be terminated with master abort. Therefore master-aborts during Special Cycle

commands are not considered errors, and are never logged or reported.

When the PXB performs a master abort, if the command was not a Special cycle, it will log the

event by setting the

PCISTS

register’s Received Master Abort (

RMA

) bit. The PXB then has two

options for generating a response.

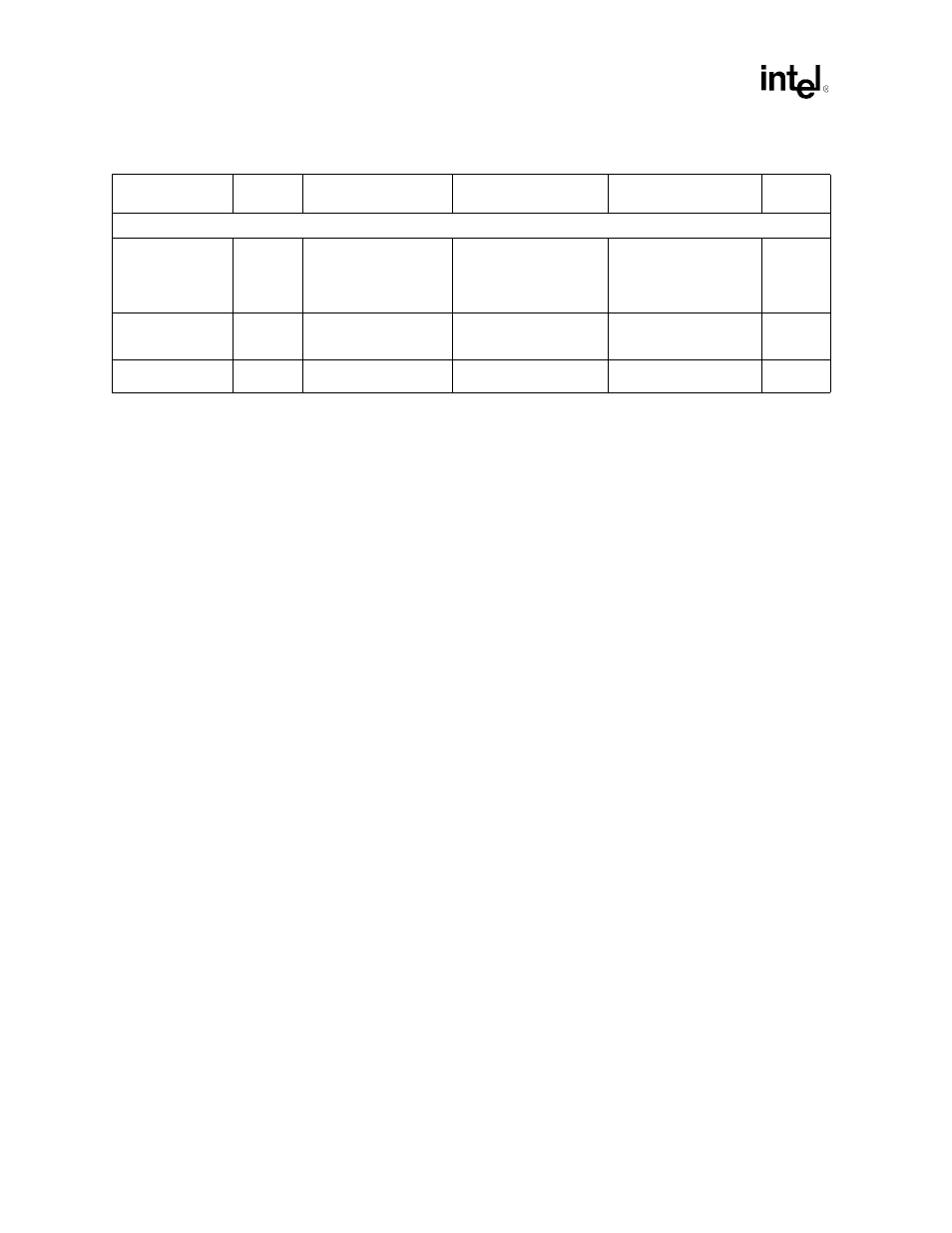

Detected as PCI Target

PCI Par-err on

Address from Card

PXB

Accept address as sent

and process as if parity

were good.

Conditionally assert

SERR#.

PCISTS[PE], PCISTS

[SSE], ERRSTS[2]

Nothing

SERRE

PCI Par-err on

Data for an IB Write

PXB

Set Status. Drive

PERR#. Pass data with

good parity to Expander.

ERRSTS [5]

Nothing

PERR# Asserted

by Card

card

Optionally turned to

SERR# by PXB.

ERRSTS[6],

PCISTS[DPE]

Nothing

Table 6-1. Error Cases (Cont’d)

Error

Chip

Detecting

System

Action

Status

Register

Log

Register

Qualifier