9 sid–subsystem id (function 3), 10 intln–interrupt line register (function 3), 11 intpn–interrupt pin (function 3) – Intel 460GX User Manual

Page 263: 12 host configuration

Intel® 460GX Chipset Software Developer’s Manual

14-5

SM Bus Controller Configuration

14.2.9

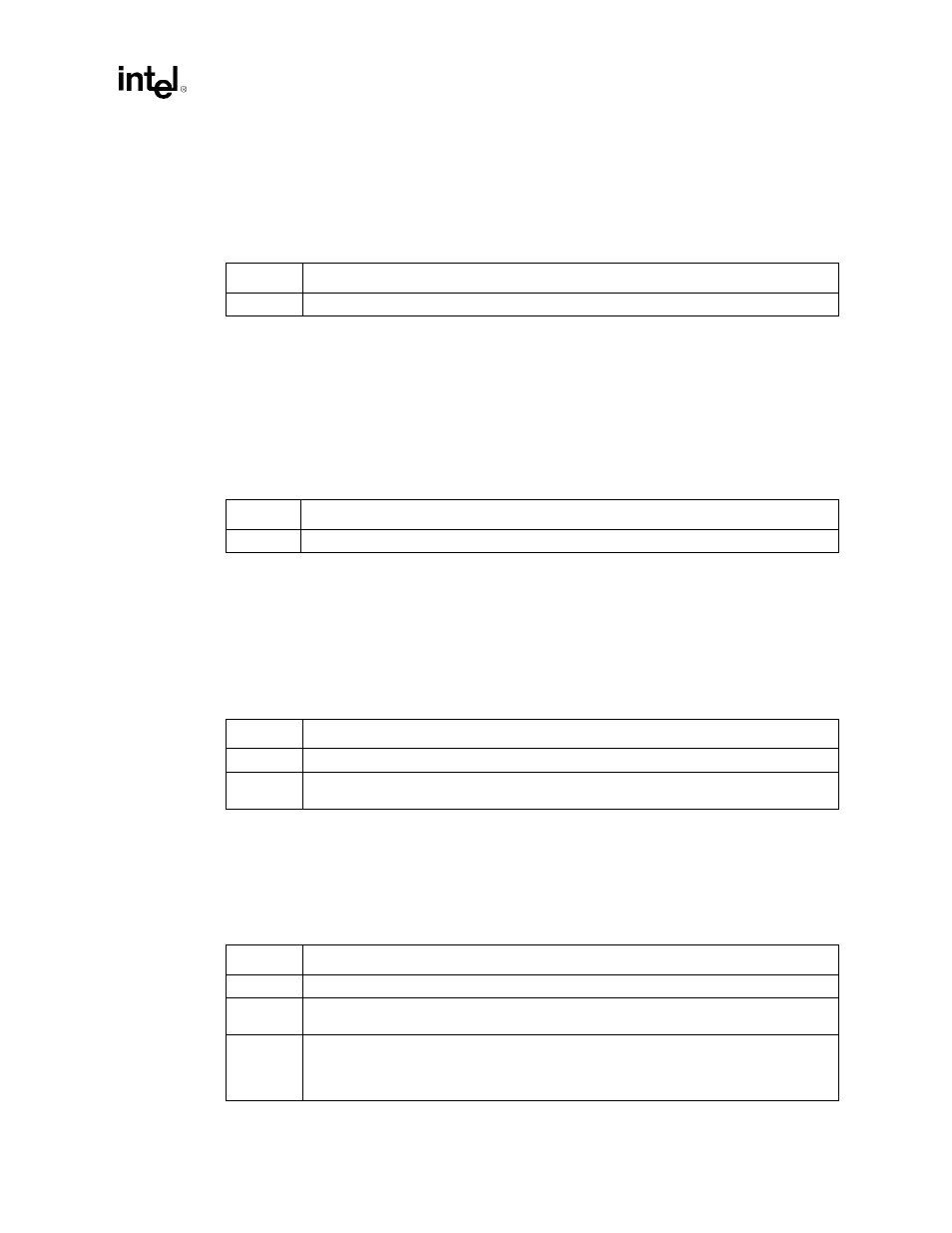

SID–Subsystem ID (Function 3)

Address:

2E-2Fh

Default Value:

0000h

Attribute:

Read only

14.2.10

INTLN–Interrupt Line Register (Function 3)

Address Offset:

3Ch

Default Value:

00h

Attribute:

Read/Write

Software programs this register with interrupt information concerning the Power Management

module.

14.2.11

INTPN–Interrupt Pin (Function 3)

Address Offset:

3Dh

Default Value:

02h

Attribute:

Read only

This register indicates that PCI interrupt PIRQB# is used for the Power Management module.

14.2.12

Host Configuration

Address Offset:

40h

Default Value:

00h

Attribute:

Read/Write

Bit Description

15:0 Subsystem

ID.

Bit

Description

7:0

Interrupt Line. The value in this register has no affect on IFB hardware operations.

Bit

Description

7:3

Reserved.

2:0

Serial Bus Module Interrupt Routing. This field is hardwired to 02h to indicate that PCI

interrupt pin PIRQB# is used.

Bit

Description

7:2

Reserved.

1

SMI_EN: When this bit is set, any source of an SMB interrupt will instead be routed to generate

an SMI#. This bit will only take effect if the INTREN bit is set in I/O space.

0

HST_EN: When set, the SMB Host Controller interface is enabled to execute commands. The

HST_INT_EN bit needs to be enabled in order for the SMB Host Controller to interrupt or SMI#.

Additionally, the SMB Host Controller will not respond to any new requests until all interrupt

requests have been. The HST_EN bit does not affect the SMB Slave Port.