10 ultra dma system software considerations, 10 ultra dma system software considerations -16 – Intel 460GX User Manual

Page 186

IFB Usage Considerations

10-16

Intel® 460GX Chipset Software Developer’s Manual

In the above configuration, none of the drives supports Ultra DMA. Only Non-ultra DMA and Fast

PIO support will be enabled on each drive.

10.5.10

Ultra DMA System Software Considerations

This section outlines some of the key system considerations for systems where Ultra DMA

operation is enabled.

The following components shall comprise a Ultra DMA/33 System:

1. Ultra DMA/33-capable Host IDE Controller.

2. Ultra DMA/33-capable ATA/ATAPI Devices.

3. Ultra DMA/33 Aware firmware and /or System Initialization Software.

4. Ultra DMA/33 Aware Device Driver.

Two of the aforementioned components are software based with specific requirements: Item #3,

Ultra DMA/33 Aware firmware and/or System Initialization Software; and Item #4, Ultra DMA/33

Aware Device Driver .

Ultra DMA/33 Aware firmware and/or System Initialization Software shall:

1. Identify Ultra DMA/33 capable devices and host controllers.

2. Configure Ultra DMA/33 operation for all Ultra DMA/33 capable devices and host

controllers.

3. Preserve Ultra DMA/33 configuration across reset states, restoring Ultra DMA/33 operation

(described in Item #2) as necessary.

Ultra DMA/33 Aware Device Drivers shall:

I. Provide support for PCI Bus Master IDE Operation (SFF8038i).

A. Identify system configured for PCI Bus Master IDE operation.

1. Identify PCI Bus Master IDE and Ultra DMA/33 capable devices and host

controllers.

2. Utilize PCI Bus Master IDE when it determines that Host Controller and ATA/

ATAPI devices have fulfilled device driver-specific, configuration requirements for

PCI Bus Master IDE operation.

B. Perform data transfer commands with PCI Bus Master IDE on devices, host controllers

that support PCI Bus Master IDE.

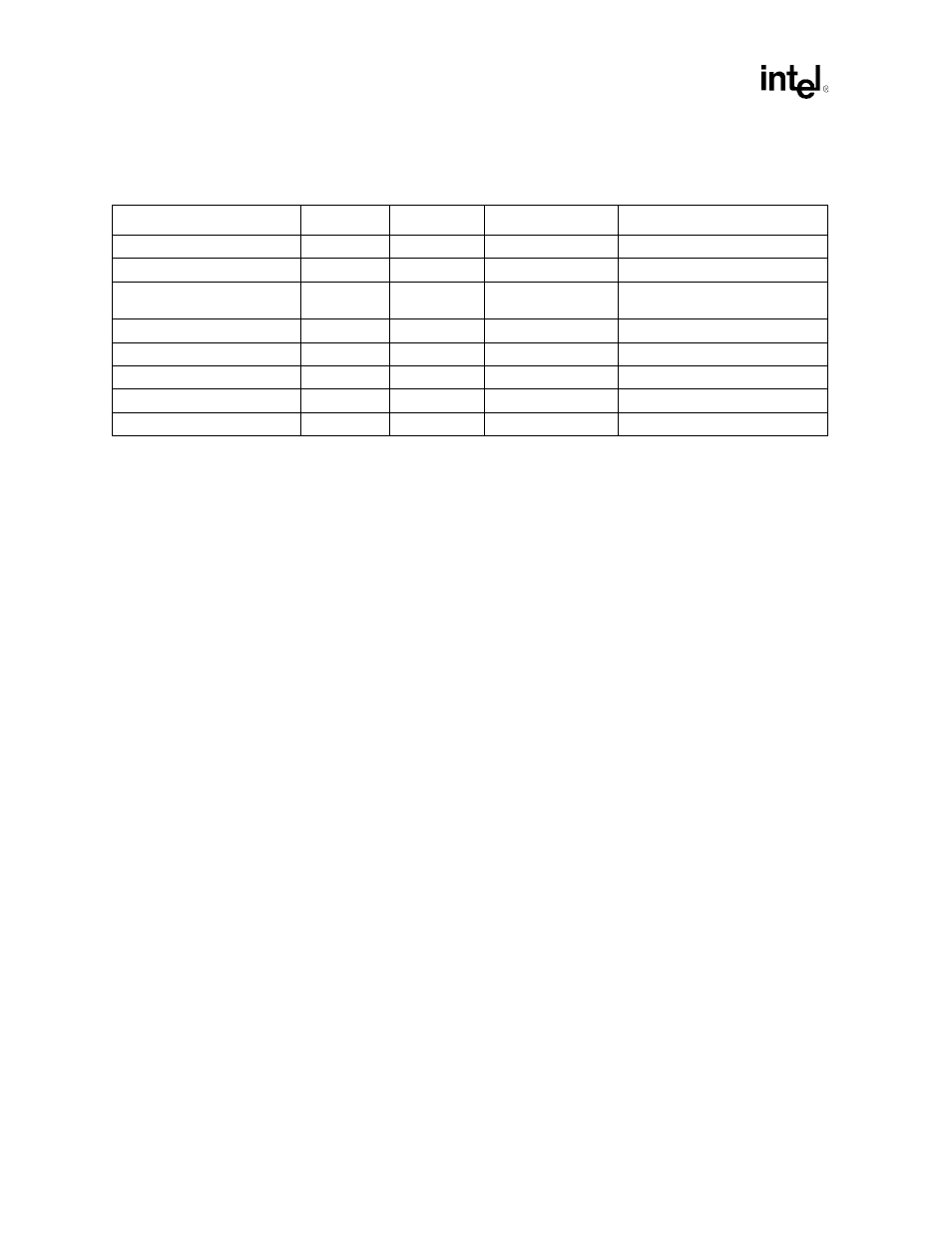

Register

Type

Offset

Value

Comments

PCI Command Register

PCI

04h

0005h

Ensure that bits 0 and 2 are ‘1’.

PCI Master Latency Timer

PCI

0Dh

System dependent

PCI Bus Master IDE Base I/O

Address

PCI

20-23h

System dependent

Ensure that bit 0 (of register value)

is ‘1’.

IDE Timing Register 1

PCI

40-41h

E377h

Mode config. for Primary

IDE Timing Register 2

PCI

42-43h

A103h

Mode config. for Secondary

Secondary IDE Timing Register

PCI

44h

0Bh

Ultra DMA Control Register

PCI

48h

00h

Ultra DMA is disabled for all drives.

Ultra DMA Timing Register

PCI

4A-4Bh

0000h