Memory-mapped register summary -47, Table 2-6, 1 i/o (x)apic id register (00h) – Intel 460GX User Manual

Page 67

Intel® 460GX Chipset Software Developer’s Manual

2-47

Register Descriptions

2.6.3.1

I/O (x)APIC ID Register (00h)

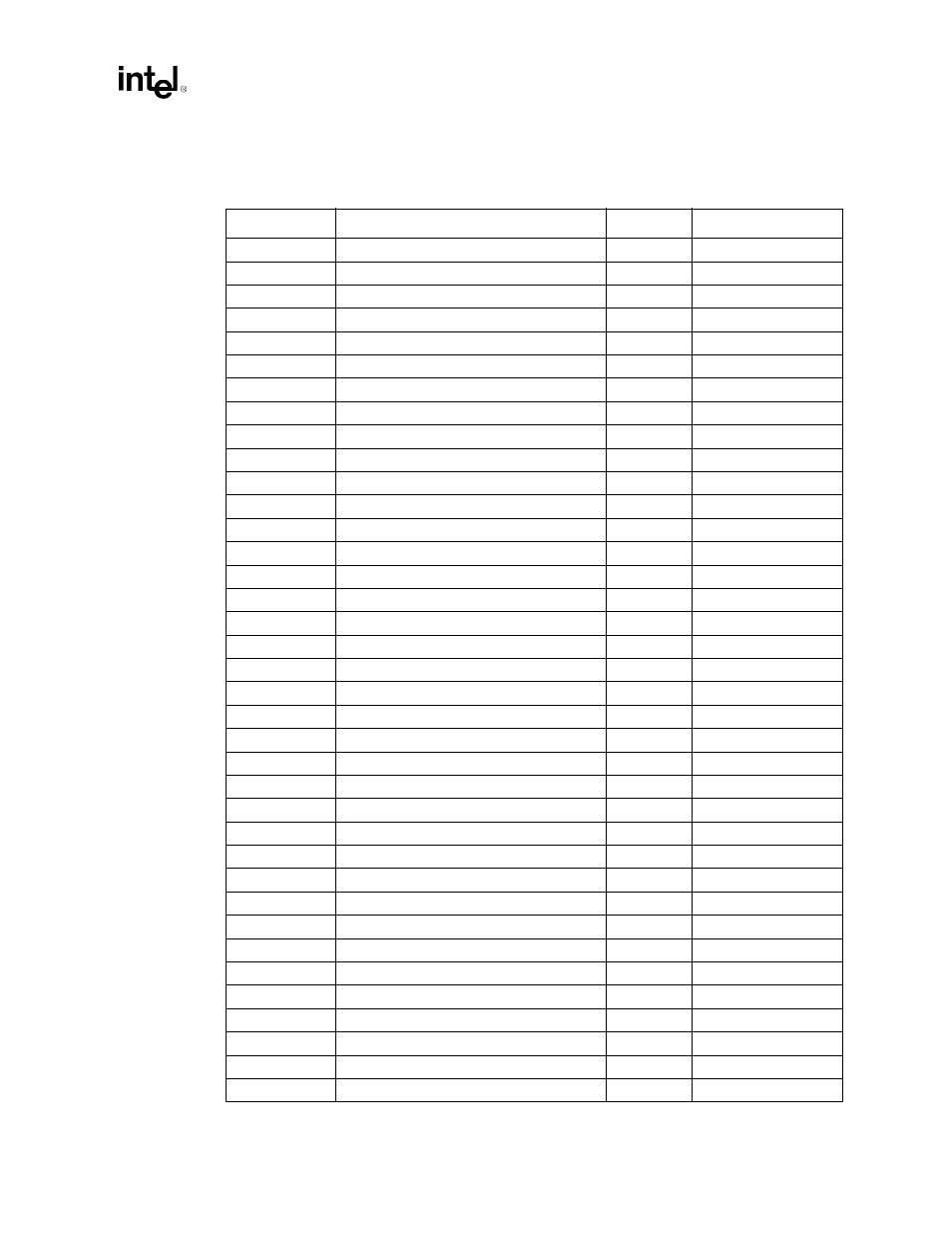

Table 2-6. Memory-mapped Register Summary

Offset

Name

Access

Default Value

00h

I/O (x)APIC ID Register

R/W

00000000h

01h

I/O (x)APIC Version Register

R/O

003F00vvh

a

02h

I/O (x)APIC Arbitration ID Register

R/O

00000000h

03h-0Fh

Reserved

R/O

00000000h

10h

RTE 0

R/W

00000000_00010000h

12h

RTE 1

R/W

00000000_00010000h

14h

RTE 2

R/W

00000000_00010000h

16h

RTE 3

R/W

00000000_00010000h

18h

RTE 4

R/W

00000000_00010000h

1Ah

RTE 5

R/W

00000000_00010000h

1Ch

RTE 6

R/W

00000000_00010000h

1Eh

RTE 7

R/W

00000000_00010000h

20h

RTE 8

R/W

00000000_00010000h

22h

RTE 9

R/W

00000000_00010000h

24h

RTE 10

R/W

00000000_00010000h

26h

RTE 11

R/W

00000000_00010000h

28h

RTE 12

R/W

00000000_00010000h

2Ah

RTE 13

R/W

00000000_00010000h

2Ch

RTE 14

R/W

00000000_00010000h

2Eh

RTE 15

R/W

00000000_00010000h

30h

RTE 16

R/W

00000000_00010000h

32h

RTE 17

R/W

00000000_00010000h

34h

RTE 18

R/W

00000000_00010000h

36h

RTE 19

R/W

00000000_00010000h

38h

RTE 20

R/W

00000000_00010000h

3Ah

RTE 21

R/W

00000000_00010000h

3Ch

RTE 22

R/W

00000000_00010000h

3Eh

RTE 23

R/W

00000000_00010000h

40h

RTE 24

R/W

00000000_00010000h

42h

RTE 25

R/W

00000000_00010000h

44h

RTE 26

R/W

00000000_00010000h

46h

RTE 27

R/W

00000000_00010000h

48h

RTE 28

R/W

00000000_00010000h

4Ah

RTE 29

R/W

00000000_00010000h

4Ch

RTE 30

R/W

00000000_00010000h

4Eh

RTE 31

R/W

00000000_00010000h

50h

RTE 32

R/W

00000000_00010000h