Intel 460GX User Manual

Page 174

IFB Usage Considerations

10-4

Intel® 460GX Chipset Software Developer’s Manual

For IFB IDE Timing Configuration, each of the following things must be determined:

•

Drive Type: ATAPI or ATA (non-ATAPI)

•

Best DMA Capability

•

Best Ultra DMA Capability OR

•

Best Multi Word DMA Capability (if Ultra DMA not supported) OR

•

Best Single Word DMA Capability (if neither Ultra DMA nor Multi Word DMA supported)

•

Best PIO Capability

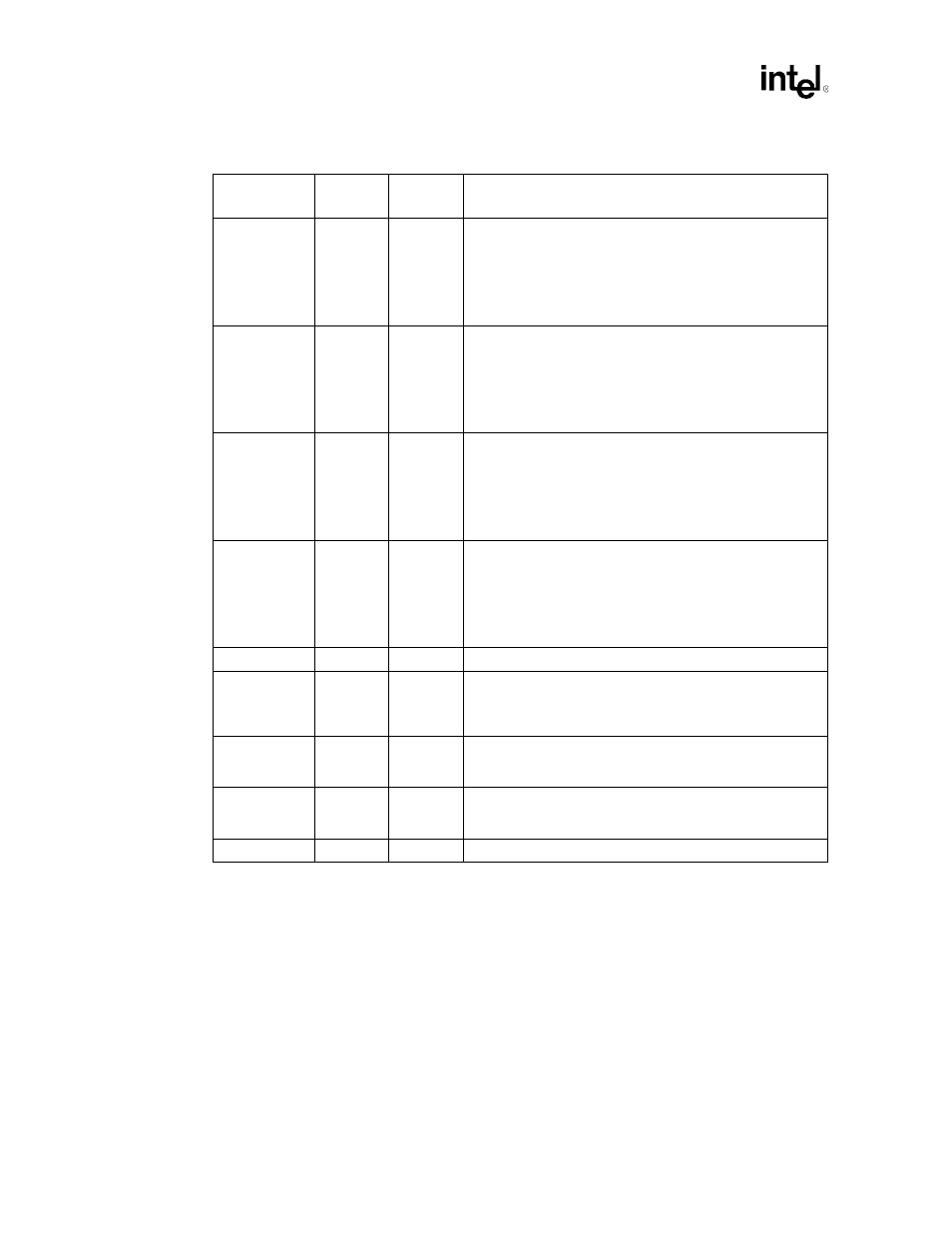

DMA

62

10:8

Single Word DMA Modes Active

bit 10: 1: Single Word DMA Mode 2 is active

0: Single Word DMA Mode 2 is not active

bit 9: 1: Single Word DMA Mode 1 is active

0: Single Word DMA Mode 1 is not active

bit 8: 1: Single Word DMA Mode 0 is active

0: Single Word DMA Mode 0 is not active

DMA

62

2:0

Single Word DMA Modes Supported

bit 2: 1: Single Word DMA Mode 2 is supported

0: Single Word DMA Mode 2 is not supported

bit 1: 1: Single Word DMA Mode 1 is supported

0: Single Word DMA Mode 1 is not supported

bit 0: 1: Single Word DMA Mode 0 is supported

0: Single Word DMA Mode 0 is not supported

DMA

63

10:8

Multi Word DMA Modes Active

bit 10: 1: Multi Word DMA Mode 2 is active

0: Multi Word DMA Mode 2 is not active

bit 9: 1: Multi Word DMA Mode 1 is active

0: Multi Word DMA Mode 1 is not active

bit 8: 1: Multi Word DMA Mode 0 is active

0: Multi Word DMA Mode 0 is not active

DMA

63

2:0

Multi Word DMA Modes Supported

bit 2: 1: Multi Word DMA Mode 2 is supported

0: Multi Word DMA Mode 2 is not supported

bit 1: 1: Multi Word DMA Mode 1 is supported

0: Multi Word DMA Mode 1 is not supported

bit 0: 1: Multi Word DMA Mode 0 is supported

0: Multi Word DMA Mode 0 is not supported

DMA

65

15:0

Minimum Multi Word DMA Transfer Cycle Time Per Word

PIO

51

15:8

PIO Data Transfer Cycle Timing Mode Supported

00h: PIO0

01h: PIO1

02h: PIO2

PIO, DMA

53

1

Field Validity

0: the fields reported in words 64-70 are not valid

1: the fields reported in word 64-70 are valid

PIO

64

7:0

Advanced Flow Control PIO Transfer Modes Supported

bit 0: PIO3 (w/IORDY Flow Control)

bit 1: PIO4 (w/IORDY Flow Control)

PIO

68

15:0

Minimum PIO Transfer Cycle Time with IORDY Flow Control

Table 10-1. Identify Device Information Used for Determining Drive Capabilities (Cont’d)

Capability

Word

Offset

Bits

Field