4 smbhstcmd–smbus host command register (i/o), 5 smbhstadd–smbus host address register (i/o), 6 smbhstdat0–smbus host data 0 register (i/o) – Intel 460GX User Manual

Page 267

Intel® 460GX Chipset Software Developer’s Manual

14-9

SM Bus Controller Configuration

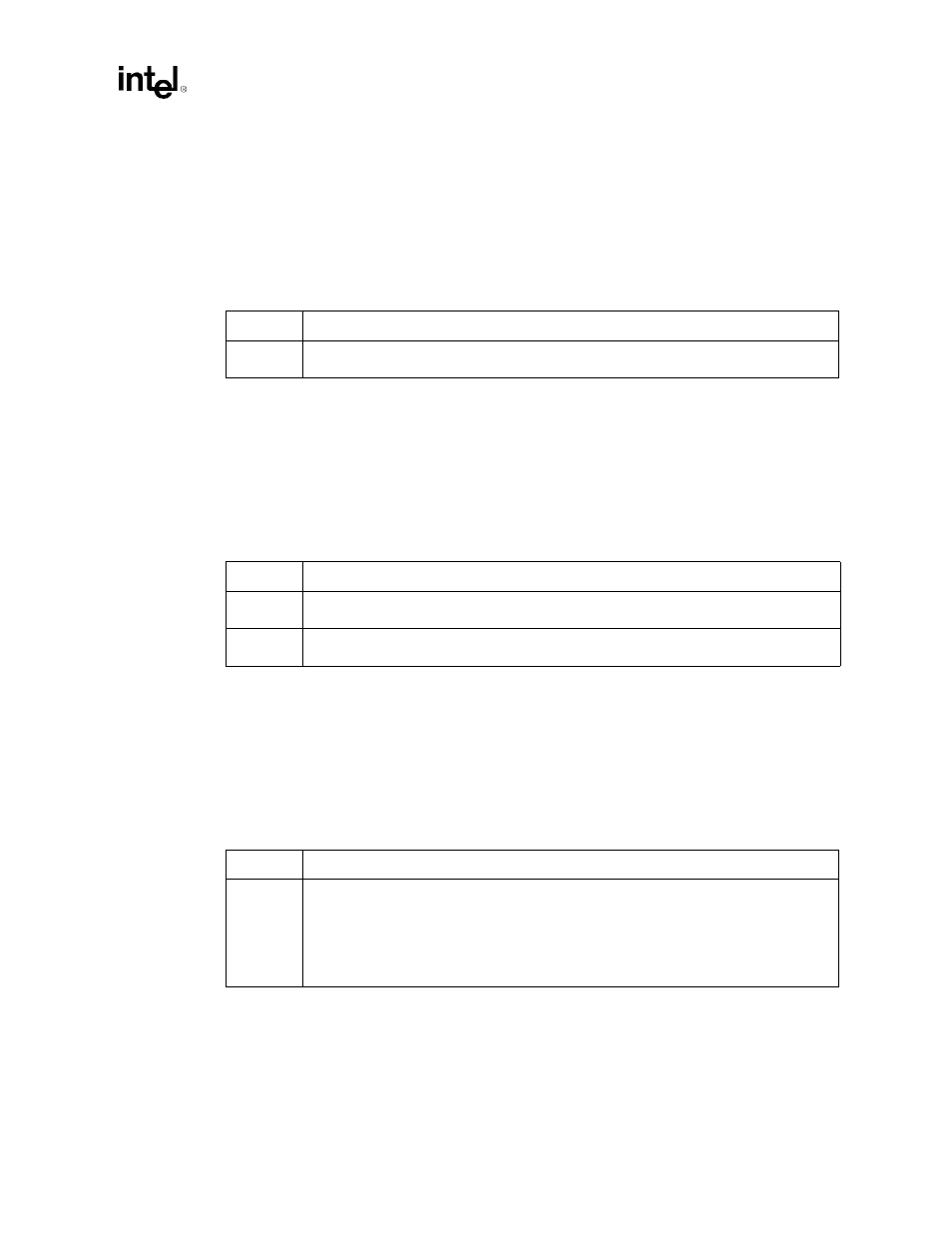

14.3.4

smbhstcmd–SMBus Host Command Register (I/O)

I/O Address:

Base + (03h)

Default Value:

00h

Attribute:

Read/Write

This register is transmitted by the SMBus controller host interface in the command field of the

SMBus protocol.

14.3.5

smbhstadd–SMBus Host Address Register (I/O)

I/O Address:

Base + (04h)

Default Value:

00h

Attribute:

Read/Write

This register is transmitted by the SMBus controller host interface in the slave address field of the

SMBus protocol.

14.3.6

smbhstdat0–SMBus Host Data 0 Register (I/O)

I/O Address:

Base + (05h)

Default Value:

00h

Attribute:

Read/Write

This register is transmitted by the SMBus controller host interface in the Data0 field of the SMBus

protocol.

Bit

Description

7:0

SMBus Host Command (HST_CMD)–R/W. This field contains the data transmitted in the

command field of SMBus host transaction.

Bit

Description

7:1

SMBus Address (SMB_ADDRESS)–R/W. This field contains the 7-bit address of the targeted

slave device.

0

SMBus Read or Write (SMB_RW)–R/W. 1 = Execute a READ command. 0 = Execute a WRITE

command.

Bit

Description

7:0

SMBus Data 0 (SMBD0)–R/W. This register should be programmed with the value to be

transmitted in the Data0 field of an SMBus host interface transaction. For a block write

command, the count of the memory block should be stored in this field. The value of this register

is loaded into the block transfer count field. This register must be programmed to a value

between 1 and 32 for block command counts. A count of 0 or a count above 32 will result in

unpredictable behavior. For block reads, the count received from the SMBus device is stored

here.