14 tom–top of memory register (function 0) – Intel 460GX User Manual

Page 196

LPC/FWH Interface Configuration

11-6

Intel® 460GX Chipset Software Developer’s Manual

11.1.13

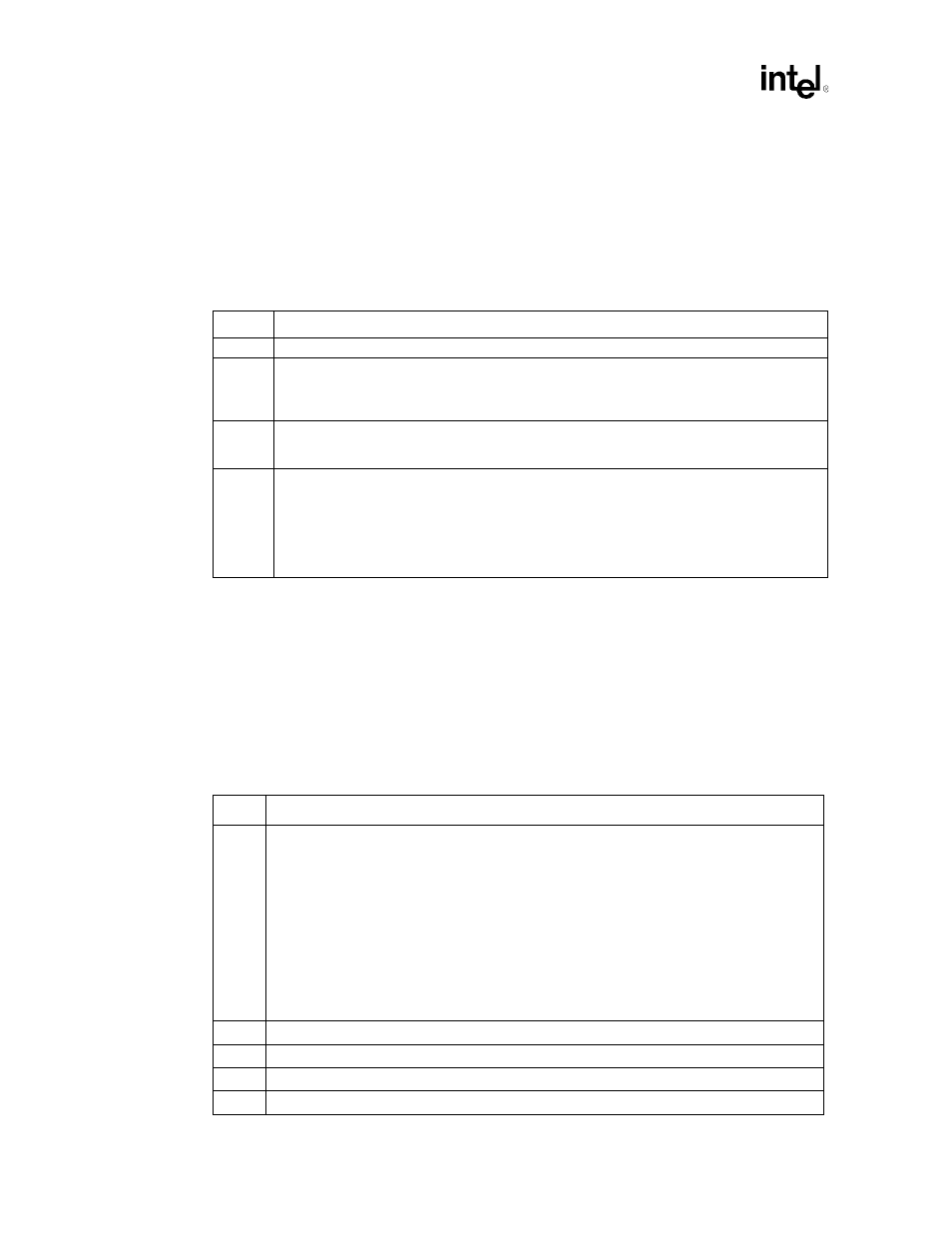

SerIRQC–Serial IRQ Control Register (Function 0)

Address Offset:

64h

Default Value:

10h

Attribute:

R/W

This register controls the Start Frame Pulse Width generated on the Serial Interrupt signal

(SERIRQ).

11.1.14

TOM–Top of Memory Register (Function 0)

Address Offset:

69h

Default Value:

02h

Attribute:

Read/Write

This register enables the forwarding of DMA memory cycles to the PCI Bus and sets the top of

main memory accessible by DMA devices. In addition, this register controls the forwarding of

DMA accesses to the lower firmware region (E0000–EFFFFh) and the 512–640 KByte main

memory region (80000–9FFFFh).

Bit

Description

7

Serial IRQ Enable. 1=Serial Interrupts are enabled. 0=Serial Interrupts disabled.

6

Serial IRQ Mode Select. When this bit is a “1”, the serial IRQ machine will be in continuous mode.

When this bit is a “0”, the serial IRQ machine will be in quiet mode. When setting the SIRQEN bit,

this bit must also be written as a one so that the first action of the serial IRQ machine will be a start

frame.

5:2

Serial IRQ Frame Size. These bits select the frame size used by the Serial IRQ logic. The default

is 0100b indicating a frame size of 21 (17+4). These bits are readable and writeable, however the

only programmed value supported by the IFB is 0100b. All other frame sizes are unsupported.

1:0

Start Frame Pulse Width. These bits define the Start Frame pulse width generated by the Serial

Interrupt control logic.

Bits[1:0] Pulse Width (PCI Clocks)

00 4 Clocks

01 6 Clocks

10 8 Clocks

11 Reserved

Bit

Description

7:4

Top Of Memory. The top of memory can be assigned in 1 Mbyte increments from 1–16 Mbytes.

DMA accesses within this region, and not in the memory hole region, are forwarded to PCI.

Bits[7:4]

0000

0001

0010

0011

0100

0101

Top of Memory

1 Mbyte

2 Mbyte

3 Mbyte

4 Mbyte

5 Mbyte

6 Mbyte

Bits[7:4]

0110

0111

1000

1001

1010

Top of Memory

7 Mbyte

8 Mbyte

9 Mbyte

10 Mbyte

11 Mbyte

Bits[7:4]

1011

1100

1101

1110

1111

Top of Memory

12 Mbyte

13 Mbyte

14 Mbyte

15 Mbyte

16 Mbyte

Note that the IFB only supports a main memory hole at the top of 16 Mbytes. Thus, If a 1 Mbyte

memory hole is created for the Host-to-PCI Bridge DRAM controller between 15 and 16 Mbytes, the

IFB Top Of Memory should be set at 15 Mbytes.

3

Reserved. Must be set to ‘0’.

2

Reserved. Must be set to ‘0’.

1

Reserved. Must be set to ‘0’.

0

Reserved.