Intel 460GX User Manual

Page 68

Register Descriptions

2-48

Intel® 460GX Chipset Software Developer’s Manual

The I/O (x)APIC ID register is read/write by software. On reset, this register’s contents are reset to

zero. This register is provided for APIC compatibility only and it does not serve any other purpose.

The PID’s (x)APIC ID register has a default value of 00000000h. This register should be

programmed with the correct (x)APIC ID value before using the PID in APIC mode. The (x)APIC

ARBID register is also written during a write to this register.

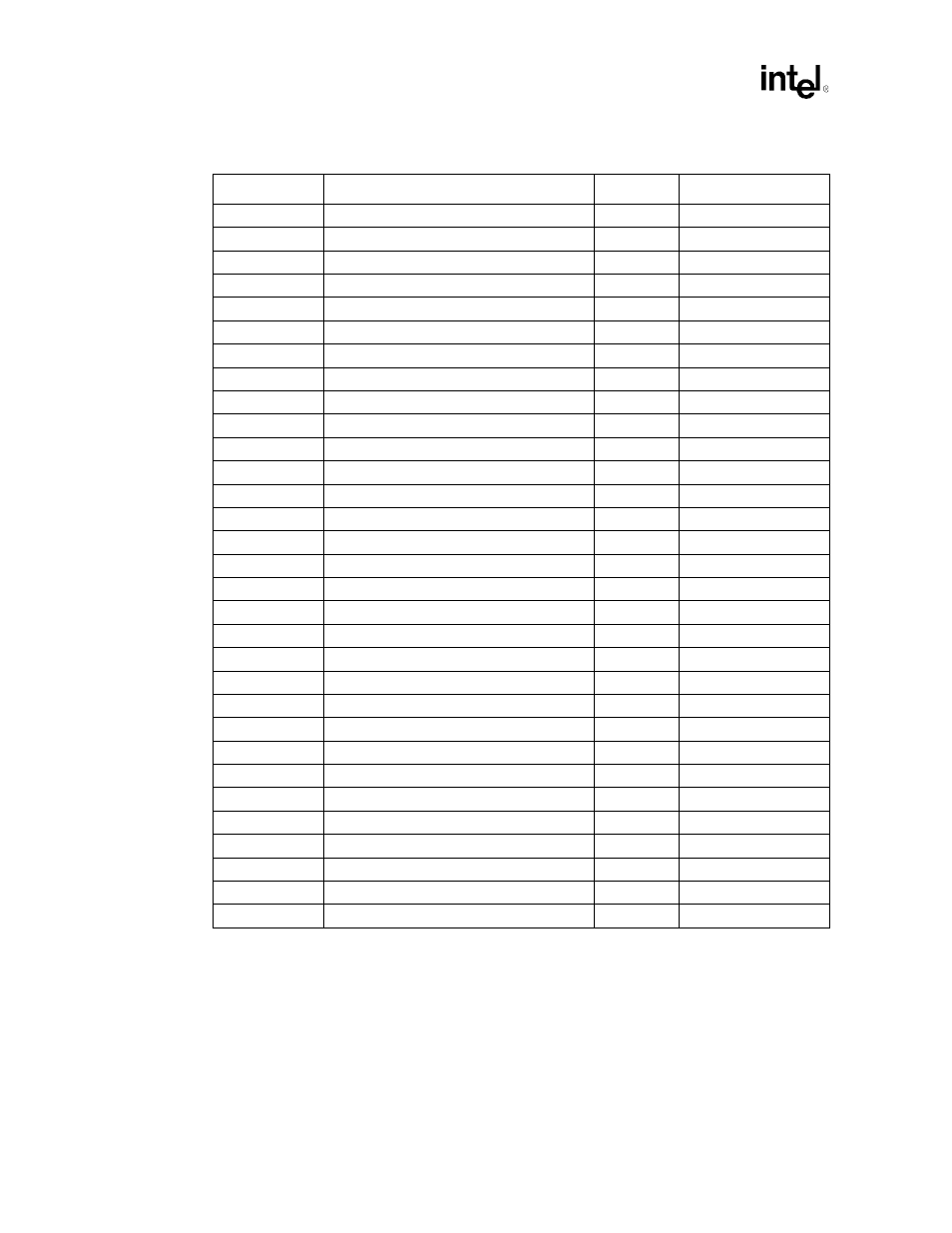

52h

RTE 33

R/W

00000000_00010000h

54h

RTE 34

R/W

00000000_00010000h

56h

RTE 35

R/W

00000000_00010000h

58h

RTE 36

R/W

00000000_00010000h

5Ah

RTE 37

R/W

00000000_00010000h

5Ch

RTE 38

R/W

00000000_00010000h

5Eh

RTE 39

R/W

00000000_00010000h

60h

RTE 40

R/W

00000000_00010000h

62h

RTE 41

R/W

00000000_00010000h

64h

RTE 42

R/W

00000000_00010000h

66h

RTE 43

R/W

00000000_00010000h

68h

RTE 44

R/W

00000000_00010000h

6Ah

RTE 45

R/W

00000000_00010000h

6Ch

RTE 46

R/W

00000000_00010000h

6Eh

RTE 47

R/W

00000000_00010000h

70h

RTE 48

R/W

00000000_00010000h

72h

RTE 49

R/W

00000000_00010000h

74h

RTE 50

R/W

00000000_00010000h

76h

RTE 51

R/W

00000000_00010000h

78h

RTE 52

R/W

00000000_00010000h

7Ah

RTE 53

R/W

00000000_00010000h

7Ch

RTE 54

R/W

00000000_00010000h

7Eh

RTE 55

R/W

00000000_00010000h

80h

RTE 56

R/W

00000000_00010000h

82h

RTE 57

R/W

00000000_00010000h

84h

RTE 58

R/W

00000000_00010000h

86h

RTE 59

R/W

00000000_00010000h

88h

RTE 60

R/W

00000000_00010000h

8Ah

RTE 61

R/W

00000000_00010000h

8Ch

RTE 62

R/W

00000000_00010000h

8Eh

RTE 63

R/W

00000000_00010000h

a. vv is 13h in APIC mode of operation, 21h in SAPIC mode of operation.

Table 2-6. Memory-mapped Register Summary (Cont’d)

Offset

Name

Access

Default Value