Supported error escalation to serr_out# -28, Supported error escalation to p(a/b)intrq# -28, Table 6-4 – Intel 460GX User Manual

Page 126: Table 6-5, 1 serr# generation

Data Integrity and Error Handling

6-28

Intel® 460GX Chipset Software Developer’s Manual

6.12.5.1

SERR# Generation

Most errors can be caused to steer the observation of the error to the signaling of an

SERR#

. The

system then has a chance to respond to the event while it continues to run. Often,

SERR#

results in

an

NMI

which itself often results in a system hang. If the WXB is configured to cause an

SERR#

the system should be configured with a usable

NMI

handler or wired in such a way that an

SERR#

is not escalated into an

NMI

.

Alternatively, the WXB can be configured to cause an

INTRQ#

interrupt or an

XBINIT#

instead of

(or in addition to) an

SERR#

. This is achieved by having any unmasked errors (errors configured

such that they might cause an

SERR#

) directed to cause the specified event, be it an

INTRQ#

or

an

XBINIT#

.

SERR# signaling itself is ultimately controlled by appropriately setting or clearing the

SERRE

bit

in the

PCICMD

register. If set then unmasked errors will result in

SERR#

being signaled.

Otherwise, even unmasked errors will not cause an

SERR#

.

Whenever the WXB actually signals an

SERR#

the

SSE

bit in the

PCISTS

register will be set. If

another agent has caused an

SERR#

then the

SES

bit in the

FEPCI

(or

NEPCI

) register will be

set.

Note:

When multiple errors, which cause an SERR# assertion, occur within a few cycles of each other,

there may not be a separate SERR# assertion for each.

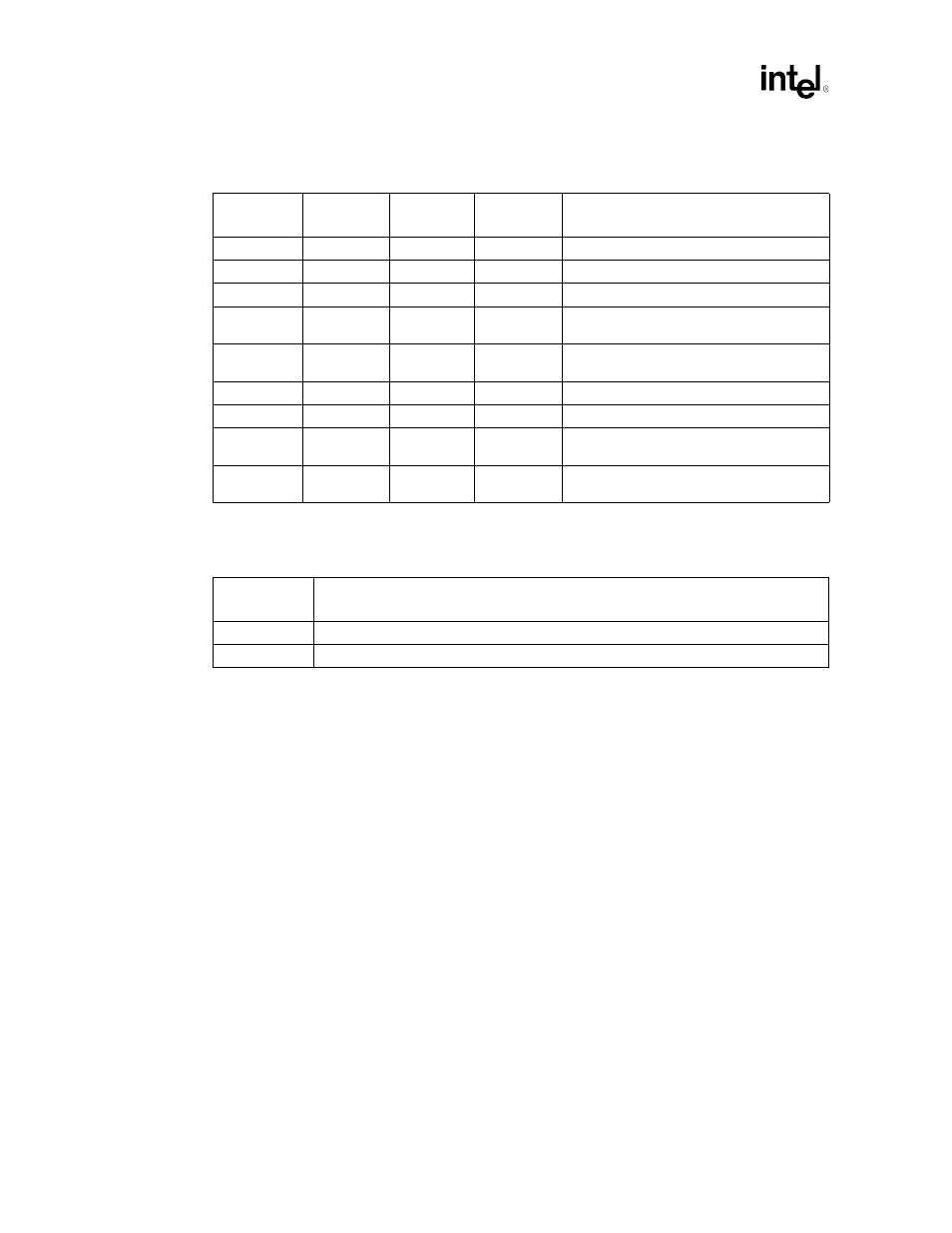

Table 6-4. Supported Error Escalation to SERR_OUT#

a

a. To obtain the listed escalation, the following settings are required: ASAPE=’1’, and ASDTE=’1’.

ASDPE

ERRCMD(11)

ASFPE

ERRCMD(9)

SERRE

PCICMD(8)

PERRE

PCICMD(6)

SERR_OUT#

Escalation

X

X

0

X

HPSERR, OSERR

0

0

1

0

HPSERR, OSERR, DTE

0

0

1

1

HPSERR, OSERR, DTE, APE

0

1

1

0

HPSERR, OSERR, DTE, OPERR, HPPERR,

PUIQ

0

1

1

1

HPSERR, OSERR, DTE, APE, OPERR,

HPPERR, PUIQ

1

0

1

0

HPSERR, OSERR, DTE, FUIQ, PCIDPE

1

0

1

1

HPSERR, OSERR, DTE, APE FUIQ, PCIDPE

1

1

1

0

HPSERR, OSERR, DTE, FUIQ, PCIDPE,

OPERR, HPPERR, PUIQ

1

1

1

1

HPSERR, OSERR, DTE, APE FUIQ, PCIDPE,

OPERR, HPPERR, PUIQ

Table 6-5. Supported Error Escalation to P(A/B)INTRQ#

IRQE

ERRCMD(13)

P(A/B)INTRQ#

0

OFF

1

OPERR, HPPERR, PUIQ