BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 89

IP Core Signals

Slave Controller

– IP Core for Xilinx FPGAs

III-77

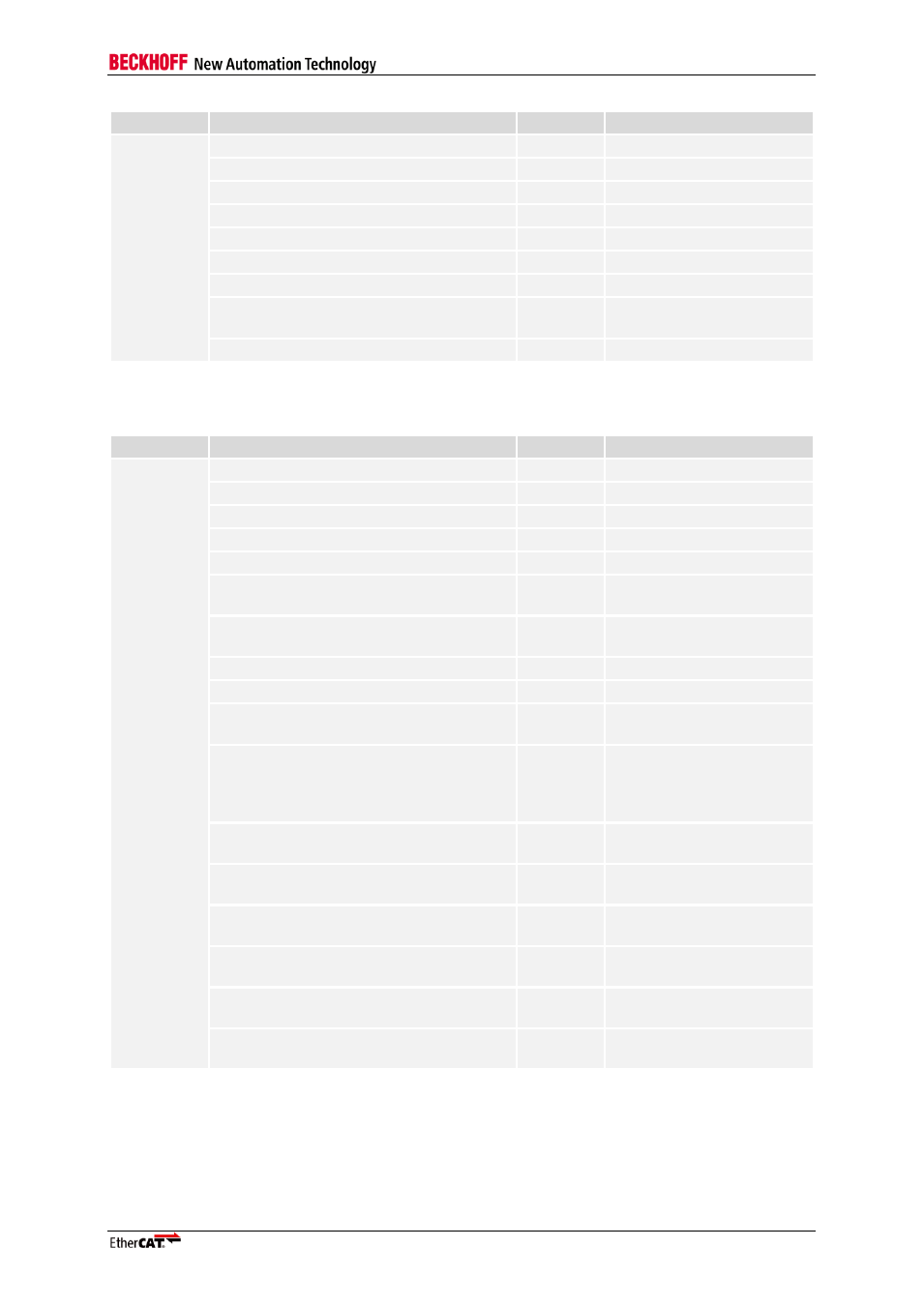

Condition

Name

Direction

Description

AXI4

PDI_AXI_BID[PDI_BUS_ID_WIDTH-1:0]

OUTPUT

Write response ID

PDI_AXI_ARID[PDI_BUS_ID_WIDTH-1:0] INPUT

Read address ID

PDI_AXI_ARLEN[7:0]

INPUT

Read length

PDI_AXI_ARSIZE[2:0]

INPUT

Read size

PDI_AXI_ARBURST[1:0]

INPUT

Read burst type

PDI_AXI_ARLOCK

INPUT

Read lock

PDI_AXI_ARCACHE[3:0]

INPUT

Read cache type

PDI_AXI_RID

[PDI_BUS_ID_WIDTH-1:0]

OUTPUT

Read data ID

PDI_AXI_RLAST

OUTPUT

Read data last

Table 35: AXI4 / AXI4 LITE PDI additional signals of XPS/EDK pcores

Condition

Name

Direction

Description

AXI4

or

AXI4 LITE

PRODUCT_ID0

GENERIC Product ID value

PRODUCT_ID1

GENERIC Product ID value

PRODUCT_ID2

GENERIC Product ID value

PRODUCT_ID3

GENERIC Product ID value

NUM_FMMU

GENERIC Number of FMMUs (0-8)

NUM_SYNC

GENERIC Numer of SyncManagers

(0-8)

SIZE_DPRAM

GENERIC Size of Process Data RAM

(0/1/2/4/8/16/32/60)

C_S_AXI_BASEADDR

GENERIC Unused AXI base address

C_S_AXI_HIGHADDR

GENERIC Unused AXI high address

PROM_CLK_O

OUTPUT

Equals

PROM_CLK

PROM_CLK_T

OUTPUT

0: enable output driver for

PROM_CLK_O

1: disable output driver for

PROM_CLK_O

PROM_DATA_I

INPUT

Equals

PROM_DATA_IN

PROM_DATA_O

OUTPUT

Equals

PROM_DATA_OUT

PROM_DATA_T

OUTPUT

Equals

NOT(PROM_DATA_ENA)

MDIO_I

INPUT

Equals

MDIO_DATA_IN

MDIO_O

OUTPUT

Equals

MDIO_DATA_OUT

MDIO_T

OUTPUT

Equals

NOT(MDIO_DATA_ENA)

NOTE: The PROM_CLK/PROM_DATA/MDIO signals with suffix _I/_O/_T are duplicates of the general tristate

signals _IN/_OUT/_ENA of PROM_CLK/PROM_DATA/MDIO_DATA. They are introduced because XPS expects

the suffixes _I/_O/_T for tristate drivers. Use either all _IN/_OUT_ENA signals or all _I/_O/_T signals. Connect

unused inputs to ‘0’ (they have in internal logic OR).