2 digital i/o configuration, Figure 19: register pdi, Digital i/o configuration – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 56

IP Core Configuration

III-44

Slave Controller

– IP Core for Xilinx FPGAs

5.1.5.2

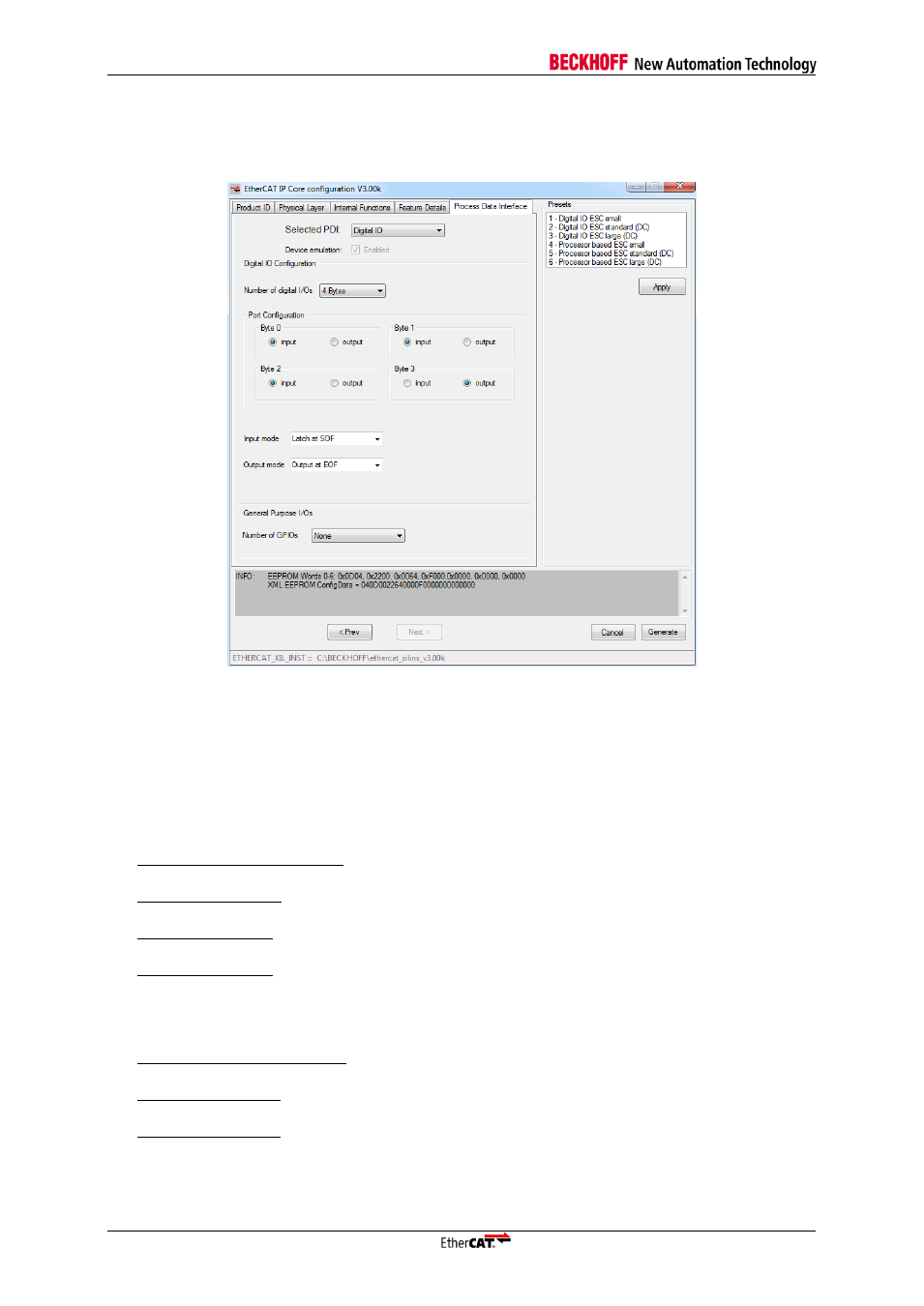

Digital I/O Configuration

The Digital I/O PDI supports up to 4 Bytes of digital I/O signals. Each byte can be assigned as input or

output byte.

Figure 19: Register PDI

– Digital I/O Configuration

Number of digital I/Os

Total number of I/Os. Possible values are 1, 2, 3 or 4 Bytes.

Port Configuration

Defining byte-wise if digital I/Os are used as input or output byte

Input Mode

Defines the latch signal which is used to take over input data.

Latch at SOF (Start of Frame)

The inputs are latched just before the data have to be written in the frame.

Latch with ext. signal

Connected to DIGI_LATCH_IN. Application controls latching

Latch at Dist-Sync0

Latch input data with distributed clock Sync0 signal

Latch at Dist-Sync1

Latch input data with distributed clock Sync1 signal

Output Mode

Defines the trigger signal for data output.

Output at EOF (End of Frame)

The outputs will be set if the frame containing the data is received complete and error free.

Output at Dist-Sync0

Outputs will be set with Sync0 signal if distributed clocks are enabled.

Output at Dist-Sync1

Outputs will be set with Sync1 signal if distributed clocks are enabled.