2 sii eeprom interface signals, 3 led signals, Sii eeprom interface signals – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 73: Led signals, Table 19: sii eeprom signals, Table 20: led signals

IP Core Signals

Slave Controller

– IP Core for Xilinx FPGAs

III-61

8.2

SII EEPROM Interface Signals

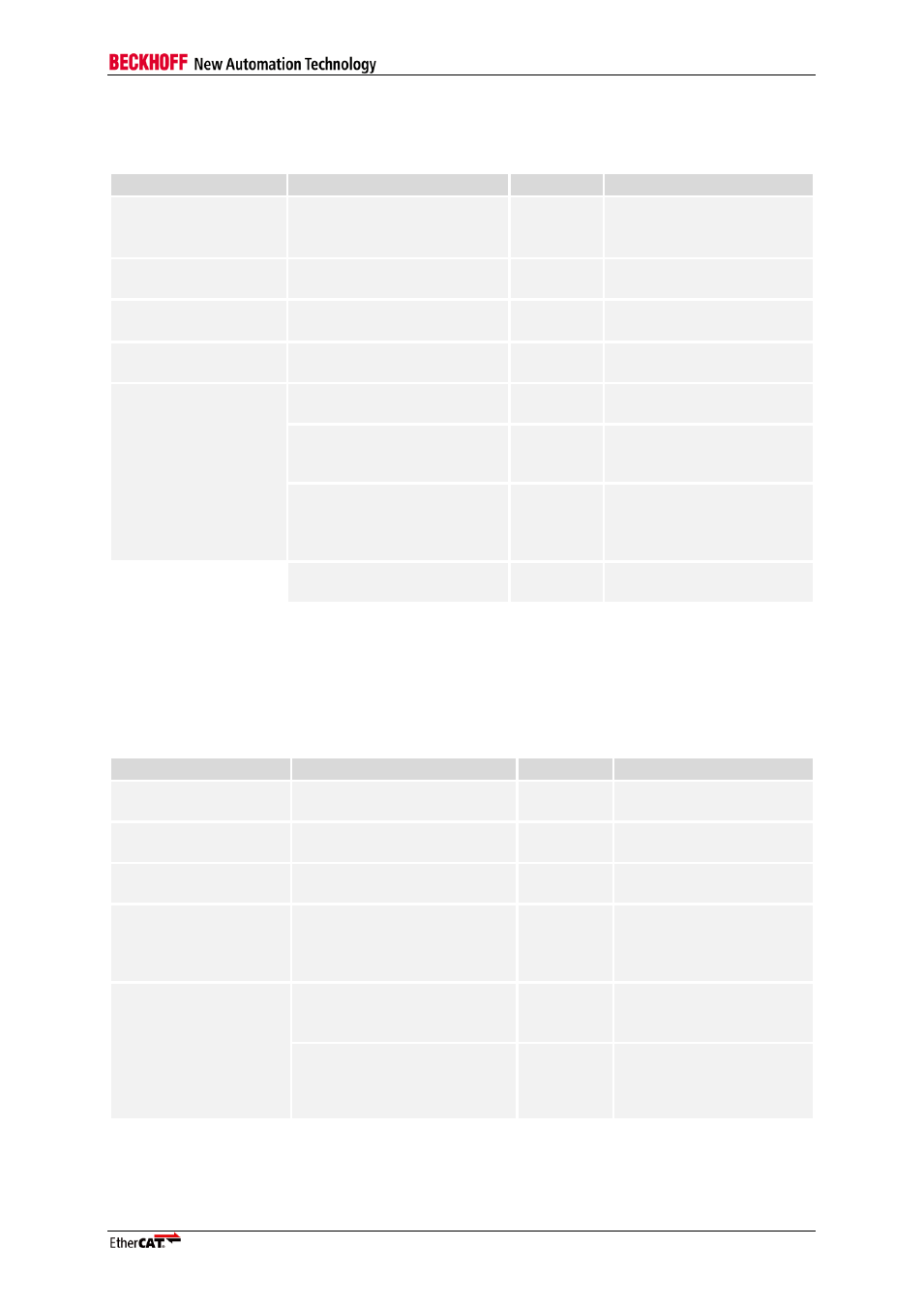

Table 19: SII EEPROM Signals

Condition

Name

Direction

Description

PROM_SIZE

INPUT

Sets EEPROM size:

0: up to 16 Kbit EEPROM

1: 32 Kbit-4 Mbit EEPROM

Tristate drivers inside

core (EEPROM/MI)

PROM_CLK

OUTPUT

EEPROM I²C Clock

(output values: 0 or Z)

External tristate drivers

for EEPROM/MI

PROM_CLK

OUTPUT

EEPROM I²C Clock

(output values: 0 or 1)

Tristate drivers inside

core (EEPROM/MI)

PROM_DATA

BIDIR

EEPROM I²C Data

External tristate drivers

for EEPROM/MI

PROM_DATA_IN

INPUT

EEPROM I²C Data:

EEPROM IP Core

PROM_DATA_OUT

OUTPUT

EEPROM I²C Data:

IP Core EEPROM

(always 0)

PROM_DATA_ENA

OUTPUT

0: disable output driver for

PROM_DATA_OUT

1: enable output driver for

PROM_DATA_OUT

PROM_LOADED

OUTPUT

0: EEPROM is not loaded

1: EEPROM is loaded

8.3

LED Signals

Table 20 lists the signals used for the LEDs. The LED signals are active high. All LEDs should be

green.

Table 20: LED Signals

Condition

Name

Direction

Description

LED_LINK_ACT[0]

OUTPUT

Link/activity LED for

ethernet port 0

2 or 3 communication

ports

LED_LINK_ACT[1]

OUTPUT

Link/activity LED for

ethernet port 1

3 communication ports

LED_LINK_ACT[2]

OUTPUT

Link/activity LED for

Ethernet port 2

RUN_LED enabled

LED_RUN

OUTPUT

RUN LED for device

status.

Always 0 if RUN LED is

deactivated.

RUN_LED enabled and

Extended RUN/ERR

LED enabled

LED_ERR

OUTPUT

ERR LED for device

status.

LED_STATE_RUN

OUTPUT

Connect to RUN pin of

dual-color STATE LED,

connect LED_ERR to

ERR pin of STATE LED

NOTE: The application ERR LED and STATE LED can alternatively be controlled by a µController if required.