5 plb processor local bus, Plb processor local bus, Table 32: plb pdi – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 85

IP Core Signals

Slave Controller

– IP Core for Xilinx FPGAs

III-73

8.6.5

PLB Processor Local Bus

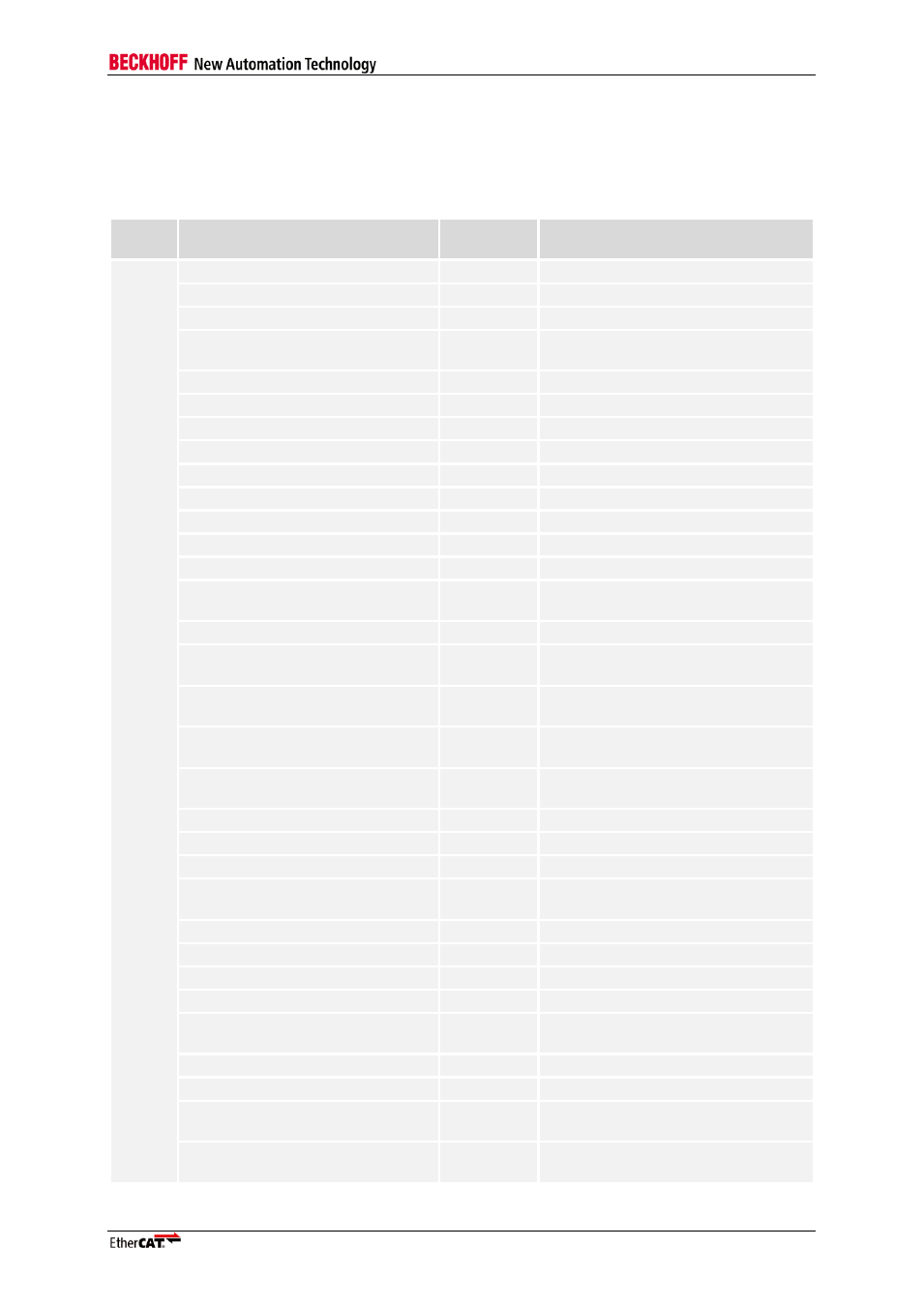

Table 32 lists the signals used with the PLB v4.6 PDI.

Table 32: PLB PDI

Condi-

tion

Name

Direction

Description

PLB

C_SPLB_BASEADDR

GENERIC

PLB base address

C_SPLB_HIGHADDR

GENERIC

PLB end address

C_SPLB_DWIDTH

GENERIC

PLB data bus width (only 32

supported)

C_SPLB_CLK_PERIOD_PS

GENERIC

PLB bus clock period in ps (

≤ 40,000)

C_SPLB_NUM_MASTERS

GENERIC

Number of masters

C_SPLB_MID_WIDTH

GENERIC

Width of master ID

C_SPLB_P2P

GENERIC

Peer-to-peer system

PDI_PLB_SPLB_Clk

INPUT

PLB bus clock

PDI_PLB_SPLB_Rst

INPUT

PLB bus reset (replaces nRESET)

PDI_PLB_ABus[0:31]

INPUT

PLB address bus

PDI_PLB_UABus[0:31]

INPUT

PLB upper address bus (not

supported)

PDI_PLB_PAValid

INPUT

PLB primary address valid

PDI_PLB_SAValid

INPUT

PLB secondary address valid

(ignored)

PDI_PLB_rdPrim

INPUT

PLB secondary to primary read

request (ignored)

PDI_PLB_wrPrim

INPUT

PLB secondary to primary write

request (ignored)

PDI_PLB_masterID

[0:C_SPLB_MID_WIDTH-1]

INPUT

PLB master ID

PDI_PLB_abort

INPUT

PLB abort bus (ignored)

PDI_PLB_busLock

INPUT

PLB bus lock (ignored)

PDI_PLB_RNW

INPUT

PLB read not write

PDI_PLB_BE

(0:(C_SPLB_DWIDTH/8)-1)

INPUT

PLB byte enables

PDI_PLB_MSize

INPUT

PLB master data bus size (ignored)

PDI_PLB_size

INPUT

PLB transfer size (must be 0000)

PDI_PLB_type

INPUT

PLB transfer type (must be 0)

PDI_PLB_lockErr

INPUT

PLB lock error (ignored)

PDI_PLB_wrDBus

(0:C_SPLB_DWIDTH-1)

INPUT

PLB write data bus

PDI_PLB_wrBurst

INPUT

PLB burst write transfer (ignored)

PDI_PLB_rdBurst

INPUT

PLB burst read transfer (ignored)

PDI_PLB_wrPendReq

INPUT

PLB pending write bus request

(ignored)

PDI_PLB_rdPendReq

INPUT

PLB pending read bus request

(ignored)