4 plb slave interface, 1 interface, Plb slave interface – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

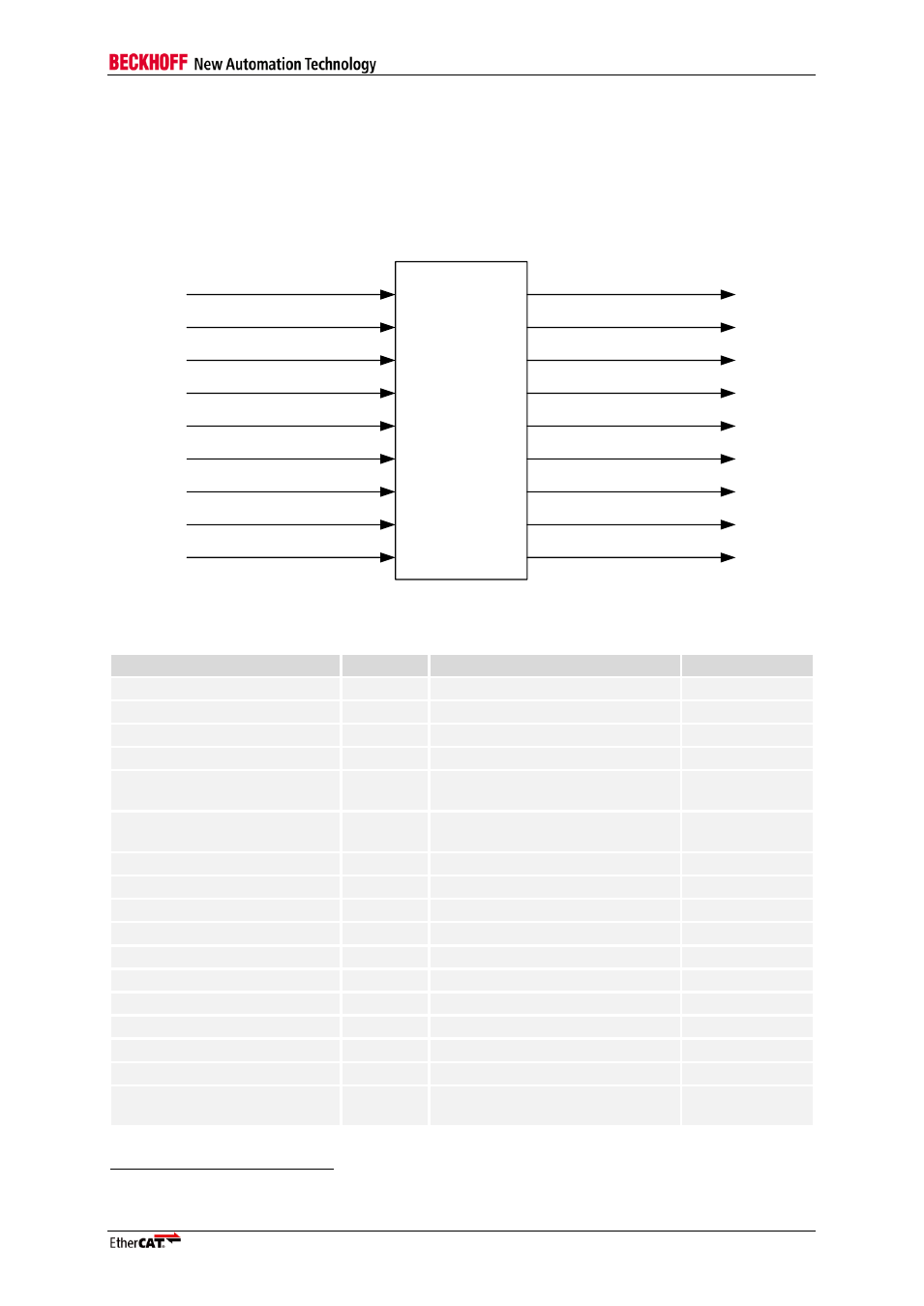

Page 129: Interface, Table 58: plb signals, Figure 57: plb signals

PDI Description

Slave Controller

– IP Core for Xilinx FPGAs

III-117

10.4 PLB Slave Interface

10.4.1 Interface

The PLB v4.6 slave PDI is selected during the IP Core configuration. The main signals of the PLB

interface are

12

:

EtherCAT

IP core

PLB_Abus[0:31]

PLB_masterID[0:x]

PLB_RNW

PLB_BE[0:3]

PLB_size[0:3]

PLB_Sl_addrAck

PLB_PAValid

PLB_Sl_wait

PLB_SPLB_CLK

PLB_Sl_wrComp

PLB_Sl_wrDAck

PLB_Sl_rdDBus[0:31]

PLB_Sl_rdDAck

PLB_wrDBus[0:31]

PLB_Sl_Mbusy[0:x]

PLB_Sl_rdComp

PLB_IRQ_MAIN

PLB_SPLB_Rst

Figure 57: PLB signals

Table 58: PLB signals

Signal

Direction

Description

Signal polarity

PLB_SPLB_Clk

IN

PLB bus clock

PLB_SPLB_Rst

IN

PLB reset

act. high

PLB_ABus[0:31]

IN

PLB address bus

PLB_PAValid

IN

PLB primary address valid

act. high

PLB_masterID

[0:PLB_MID_WIDTH-1]

IN

PLB current master identifier

PLB_RNW

IN

PLB read not write

0: Write

1: Read

PLB_BE[0:3]

IN

PLB byte enable

PLB_size[0:3]

IN

PLB transfer size (must be 0000)

PLB_wrDBus[0:31]

IN

PLB write data bus

PLB_Sl_addrAck

OUT

Slave address acknowledge

act. high

PLB_Sl_wait

OUT

Slave wait

act. high

PLB_Sl_wrDAck

OUT

Slave write data acknowledge

act. high

PLB_Sl_wrComp

OUT

Slave write transfer complete

act. high

PLB_Sl_rdDBus[0:31]

OUT

Slave read data bus

PLB_Sl_rdDAck

OUT

Slave read data acknowledge

act. high

PLB_Sl_rdComp

OUT

Slave read transfer complete

act. high

PLB_Sl_MBusy

[0: SPLB_NUM_MASTERS-1]

OUT

Slave busy

12

The prefix `PDI_` is added to the PLB interface signals for the IP Core interface. Additional signals are part of

the PLB interface, but they are not used according to Xilinx PLB v4.6 interface simplifications.