11 timing specifications, Timing specifications, Table 52: spi timing characteristics ip core – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 115

PDI Description

Slave Controller

– IP Core for Xilinx FPGAs

III-103

10.2.11 Timing specifications

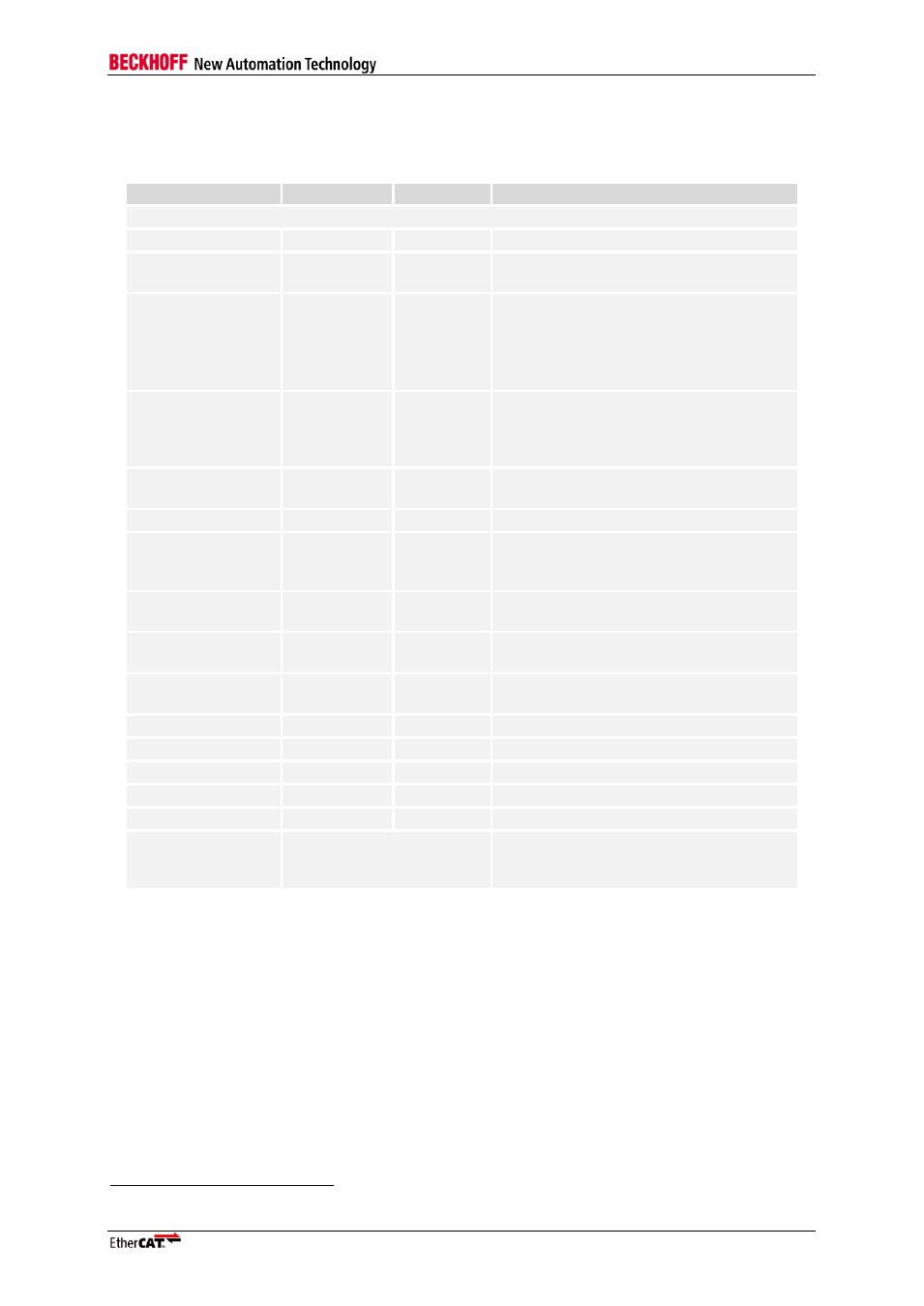

Table 52: SPI timing characteristics IP Core

Parameter

Min

Max

Comment

PRELIMINARY TIMING

t

CLK

33 ns+x

7

SPI_CLK frequency (f

CLK

≤ 30 MHz)

t

SEL_to_CLK

First SPI_CLK cycle after SPI_SEL

asserted

t

CLK_to_SEL

a) x

b) t

CLK

/2+ x

Deassertion of SPI_SEL after last

SPI_CLK cycle

a) SPI mode 0/2, SPI mode 1/3 with

normal data out sample

b) SPI mode 1/3 with late data out sample

t

read

240 ns

Only for read access between

address/command and first data byte.

Can be ignored if BUSY or Wait State

Bytes are used.

t

C0_to_BUSY_OE

t

CLK

BUSY OUT Enable assertion after sample

time of last command bit C0.

t

BUSY_valid

BUSY valid after BUSY OUT Enable

t

BUSY_OE_to_DO_valid

Only for SPI mode 0/2 with normal data

out sampling: Data byte 0 bit 7 valid after

deassertion of BUSY OUT Enable

t

SEL_to_DO_valid

Status/Interrupt Byte 0 bit 7 valid after

SPI_SEL asserted

t

SEL_to_DO_invalid

0 ns

Status/Interrupt Byte 0 bit 7 invalid after

SPI_SEL deasserted

t

STATUS_valid

Time until status of last access is valid.

Can be ignored if status is not used.

t

access_delay

Delay between SPI accesses

t

DI_setup

SPI_DI valid before SPI_CLK edge

t

DI_hold

SPI_DI valid after SPI_CLK edge

t

CLK_to_DO_valid

SPI_DO valid after SPI_CLK edge

t

CLK_to_DO_invalid

0 ns

SPI_DO invalid after SPI_CLK edge

t

IRQ_delay

160 ns

Internal delay between AL event and

SPI_IRQ output to enable correct reading

of the interrupt registers.

7

EtherCAT IP Core: time depends on synthesis results