8 ip core signals, 1 general signals, Ip core signals – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 71: General signals, Table 18: general signals

IP Core Signals

Slave Controller

– IP Core for Xilinx FPGAs

III-59

8

IP Core Signals

The available signals depend on the IP Core configuration.

8.1

General Signals

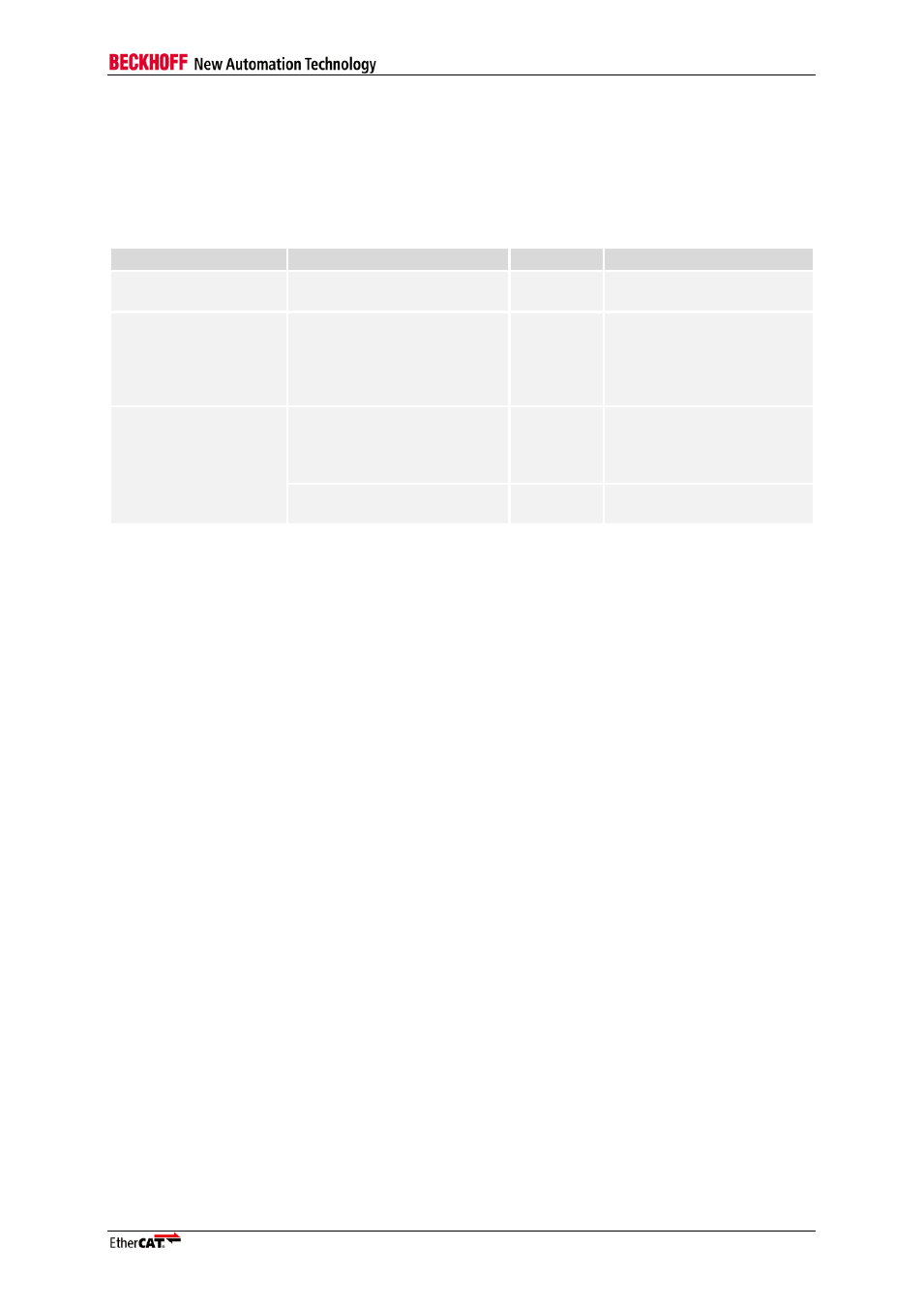

Table 18: General Signals

Condition

Name

Direction

Description

nRESET

INPUT

Resets all registers of the

IP Core, active low

Reset slave by

ECAT/PDI

RESET_OUT

OUTPUT

Reset by ECAT (reset

register 0x0040), active

high. RESET_OUT has to

trigger nRESET, which

clears RESET_OUT.

CLK25

INPUT

25 MHz clock signal from

PLL (rising edge

synchronous with rising

edge of CLK100)

CLK100

INPUT

100 MHz clock signal from

PLL

See also other documents in the category BECKHOFF Equipment:

- EP-xxxx-xxxx (19 pages)

- Bus Terminal System (19 pages)

- BK2000 (30 pages)

- LC3100 (67 pages)

- BK4000 (28 pages)

- BK3xx0 (95 pages)

- BK5000 (12 pages)

- LC5200 (32 pages)

- BK7000 (29 pages)

- BK7500 (32 pages)

- BK7300 (40 pages)

- BK8100 (26 pages)

- BC2000 (28 pages)

- BC3100 (51 pages)

- BC7300 (48 pages)

- BC8100 (36 pages)

- BC3150 (112 pages)

- KL1012 (2 pages)

- KL1114 (2 pages)

- KL1164 (1 page)

- KL1232-xxxx (4 pages)

- KL1501 (19 pages)

- KL1512 (15 pages)

- KL2521-0024 (18 pages)

- KL2512 (21 pages)

- KL2612 (4 pages)

- KL2622 (9 pages)

- KL3062 (24 pages)

- KL3064 (20 pages)

- KL4132 (19 pages)

- KL4034 (25 pages)

- KL3302 (23 pages)

- KL3351 (18 pages)

- KS3681 (43 pages)

- KL4112 (18 pages)

- KL5001 (16 pages)

- KL5051 (17 pages)

- KL5101-0012 (21 pages)

- KS5111-0000 (21 pages)

- KL5121 (19 pages)

- KL6021 (20 pages)

- KL6051 (17 pages)

- Z1000 (2 pages)

- KL6071 (12 pages)

- Z1003 (2 pages)