BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 29

Features and Registers

Slave Controller

– IP Core for Xilinx FPGAs

III-17

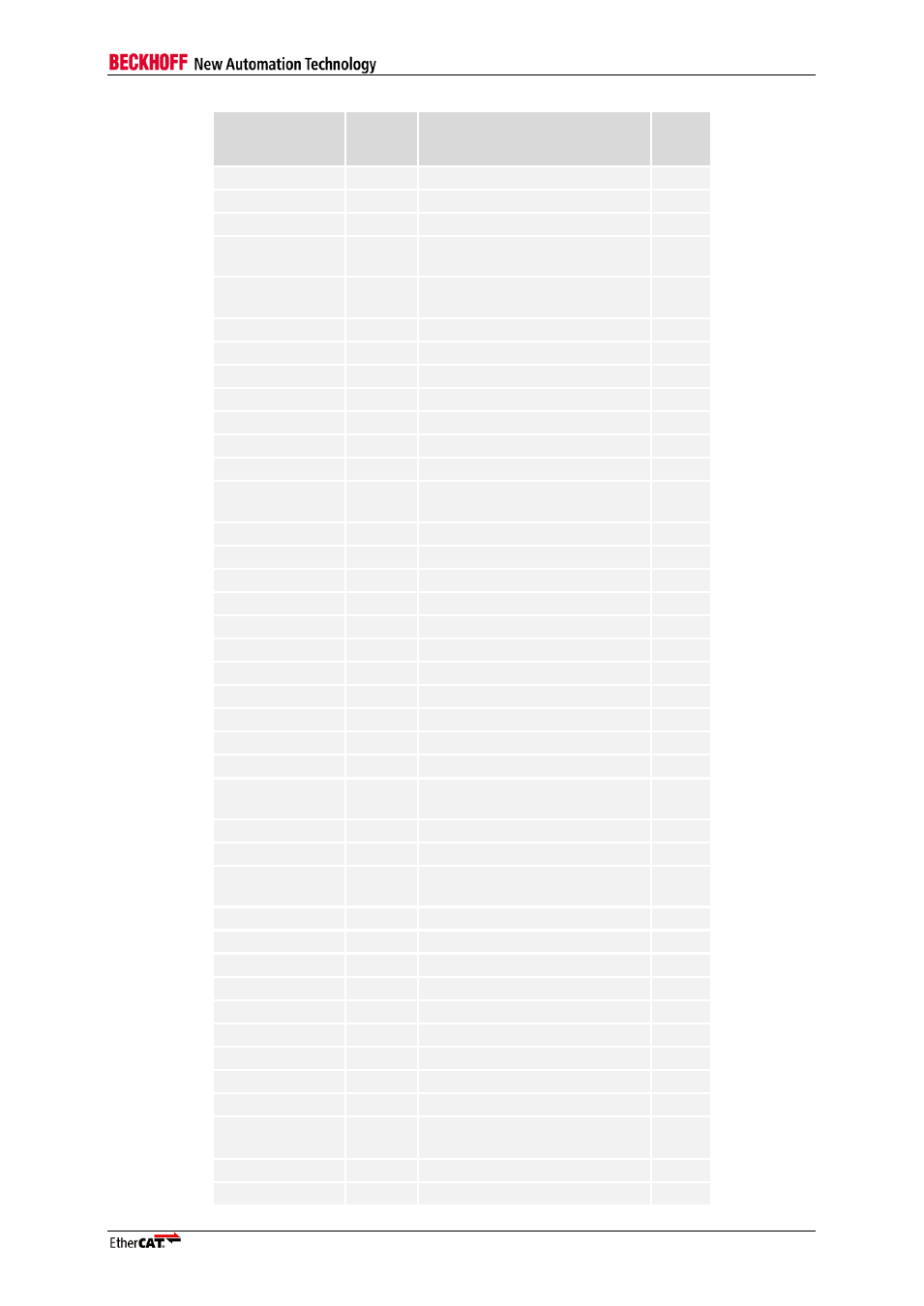

Address

Length

(Byte)

Description

IP Core

V3.00c-

V3.00k

0x0210:0x0211

2

ECAT Event Request

x

0x0220:0x0223

4

AL Event Request

x

0x0300:0x0307

4x2

Rx Error Counter[3:0]

x

0x0308:0x030B

4x1

Forwarded Rx Error

counter[3:0]

x

0x030C

1

ECAT Processing Unit Error

Counter

c

0x030D

1

PDI Error Counter

c

0x030E

1

PDI Error Code

c

0x0310:0x0313

4x1

Lost Link Counter[3:0]

c

0x0400:0x0401

2

Watchdog Divider

r/c

0x0410:0x0411

2

Watchdog Time PDI

c

0x0420:0x0421

2

Watchdog Time Process Data

x

0x0440:0x0441

2

Watchdog Status Process Data

x

0x0442

1

Watchdog Counter Process

Data

c

0x0443

1

Watchdog Counter PDI

c

0x0500:0x050F

16

SII EEPROM Interface

x

0x0510:0x0515

6

MII Management Interface

c

0x0516:0x0517

2

MII Management Access State

c

0x0518:0x051B

4

PHY Port Status[3:0]

c

0x0600:0x06FC

16x13

FMMU[15:0]

0-8

0x0800:0x087F

16x8

SyncManager[15:0]

0-8

0x0900:0x090F

4x4

DC

– Receive Times[3:0]

rt

0x0910:0x0917

8

DC

– System Time

dc

0x0918:0x091F

8

DC

– Receive Time EPU

dc

0x0920:0x0935

24

DC

– Time Loop Control Unit

dc

0x0936

1

DC

– Receive Time Latch

mode

-

0x0980

1

DC

– Cyclic Unit Control

dc

0x0981

1

DC

– Activation

dc

0x0982:0x0983

2

DC

– Pulse length of

SyncSignals

dc

0x0984

1

DC

– Activation Status

dc

0x098E:0x09A7

26

DC

– SYNC Out Unit

dc

0x09A8

1

DC

– Latch0 Control

dc

0x09A9

1

DC

– Latch1 Control

dc

0x09AE

1

DC

– Latch0 Status

dc

0x09B0:0x09B7

8

DC

– Latch0 Positive Edge

dc

0x09B8:0x09BF

8

DC

– Latch0 Negative Edge

dc

0x09C0:0x09C7

8

DC

– Latch1 Positive Edge

dc

0x09C7:0x09CF

8

DC

– Latch1 Negative Edge

dc

0x09F0:0x09F3

0x09F8:0x09FF

12

DC

– SyncManager Event

Times

c

0x0E00:0x0E03

4

Power-On Values (Bits)

-

0x0E00:0x0E07

8

Product ID

x