7 release notes, Release notes, Table 4: release notes – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 18

Overview

III-6

Slave Controller

– IP Core for Xilinx FPGAs

1.7

Release Notes

EtherCAT IP Core updates deliver feature enhancements and removed restrictions. Feature

enhancements are not mandatory regarding conformance to the EtherCAT standard. Restrictions

have to be judged whether they are relevant in the user’s configuration or not, or if workarounds are

possible.

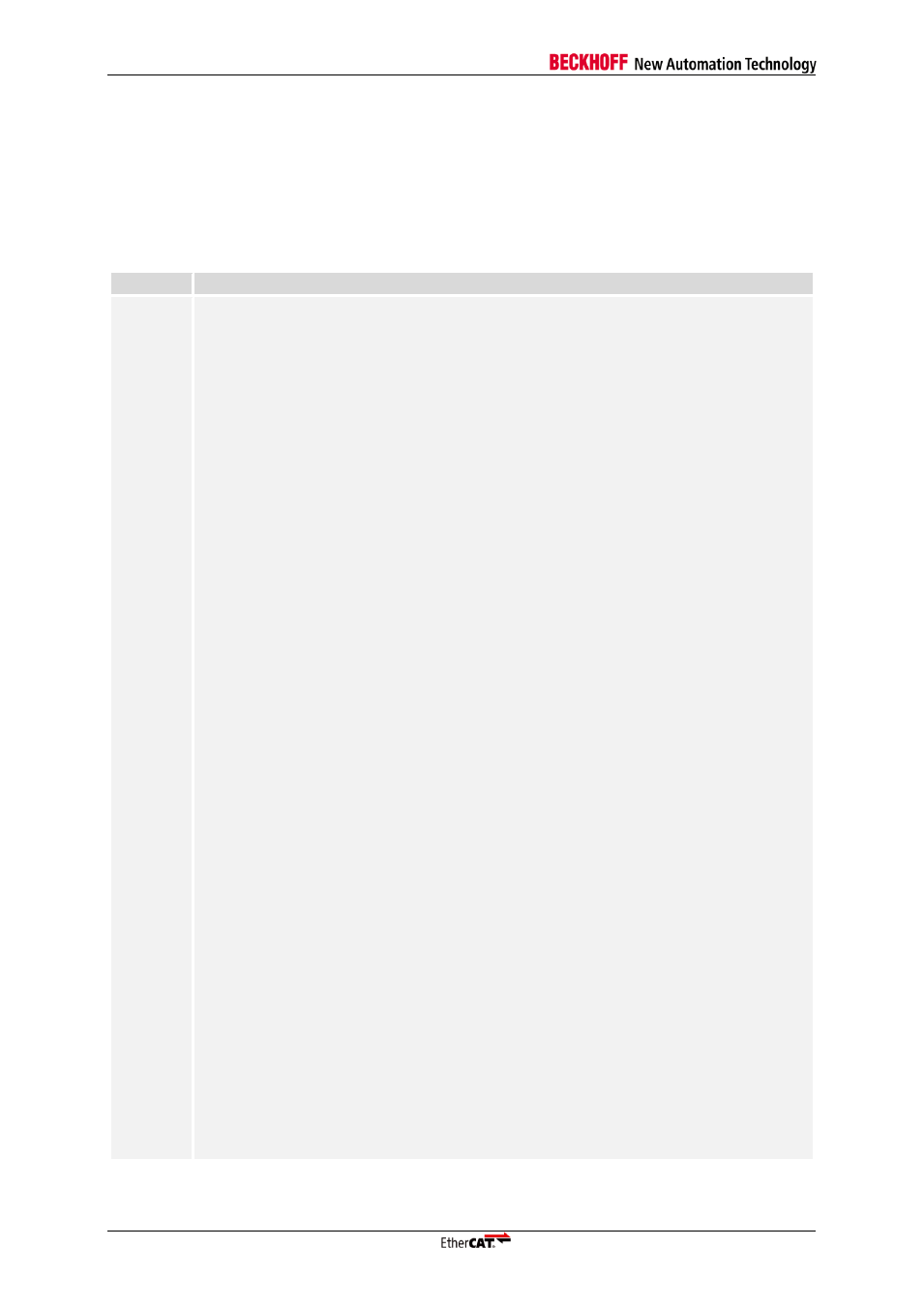

Table 4: Release notes

Version

Release notes

3.00c

(5/2013)

Update to ISE 14.3/14.4/14.5, Vivado 2013.1

Removed support for Spartan-3/-3E/-3A/-3AN/-3AN DSP, Virtex-4, and Virtex-5 due

to XST incompatibility

Removed OPB support

Removed small/medium/large register sets, added updated preset configurations

Enhancements:

Increased PDI performance

Support for 8/16/32/64 bit AXI4 and AXI4 Lite interface

Support for RGMII ports

Native support for FX PHYs

Support for individual PHY address configuration and reading out this configuration

Support for static or dynamic PHY address configuration

Support for 0 KB Process RAM, DC Sync/Latch signals individually configurable,

LED test added

Support for PDI SyncManager/IRQ acknowledge by Write command

Device emulation is now configured in the GUI statically.

MI link detection: relaxed checking of PHY register 9 (1000Base-T Master-Slave

Control register)

Restrictions of this version, which are removed in V3.00f:

The AXI PDI may occasionally write incorrect data if simultaneous read and write

accesses occur repeatedly.

RX FIFO size is not initialized by SII EEPROM

Restrictions of this version, which are removed in V3.00g:

The ERR LED does not allow overriding using the ERR LED Override register

0x0139 while AL Status register Error Indication bit 0x0130[4] is set

RMII is not supported because of wrong configuration by IPCore_Config tool

Restrictions of this version, which are removed in V3.00j:

The AXI PDI may not complete an access occasionally if overlapping read and write

accesses occur, causing the processor to wait endlessly.

The AXI PDI does not execute read accesses correctly if ARSIZE is smaller than

the AXI bus width.

Restrictions of this version, which are removed in V3.00k:

The last 4 Kbyte Process Data RAM (0xF000:0xFFFF) cannot be used in the 60

Kbyte RAM configuration.

The AXI PDI may write to wrong bytes if the write data is valid before the address,

which is typically true for AXI4LITE.

The AXI PDI may read additional bytes after the intended bytes.

The PLB PDI only supports peer-to-peer mode (C_SPLB_P2P=1), or a base

address of 0 (C_SPLB_BASEADDR=0x00000000).

The PLB PDI was generated with an invalid component declaration package.