Table 53: read/write timing diagram symbols – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 116

PDI Description

III-104

Slave Controller

– IP Core for Xilinx FPGAs

Table 53: Read/Write timing diagram symbols

Symbol

Comment

A15..A0

Address bits [15:0]

D0_7..D0_0

D1_7..D1_0

Data bits byte 0 [7:0]

Data bits byte 1 [7:0]

I0_7..I0_0

I1_7..I1_0

I2_7..I2_0

Interrupt request register 0x0220 [7:0]

Interrupt request register 0x0221 [7:0]

Interrupt request register 0x0222 [7:0]

C0_2..C0_0

C1_2..C1_0

Command 0 [2:0]

Command 1 [2:0] (3 byte addressing)

Status

0: last SPI access had errors

1: last SPI access was correct

BUSY OUT

Enable

0: No Busy output, tread is relevant

1: Busy output on SPI_DO (edge sensitive)

BUSY

0: SPI slave has finished reading first byte

1: SPI slave is busy reading first byte

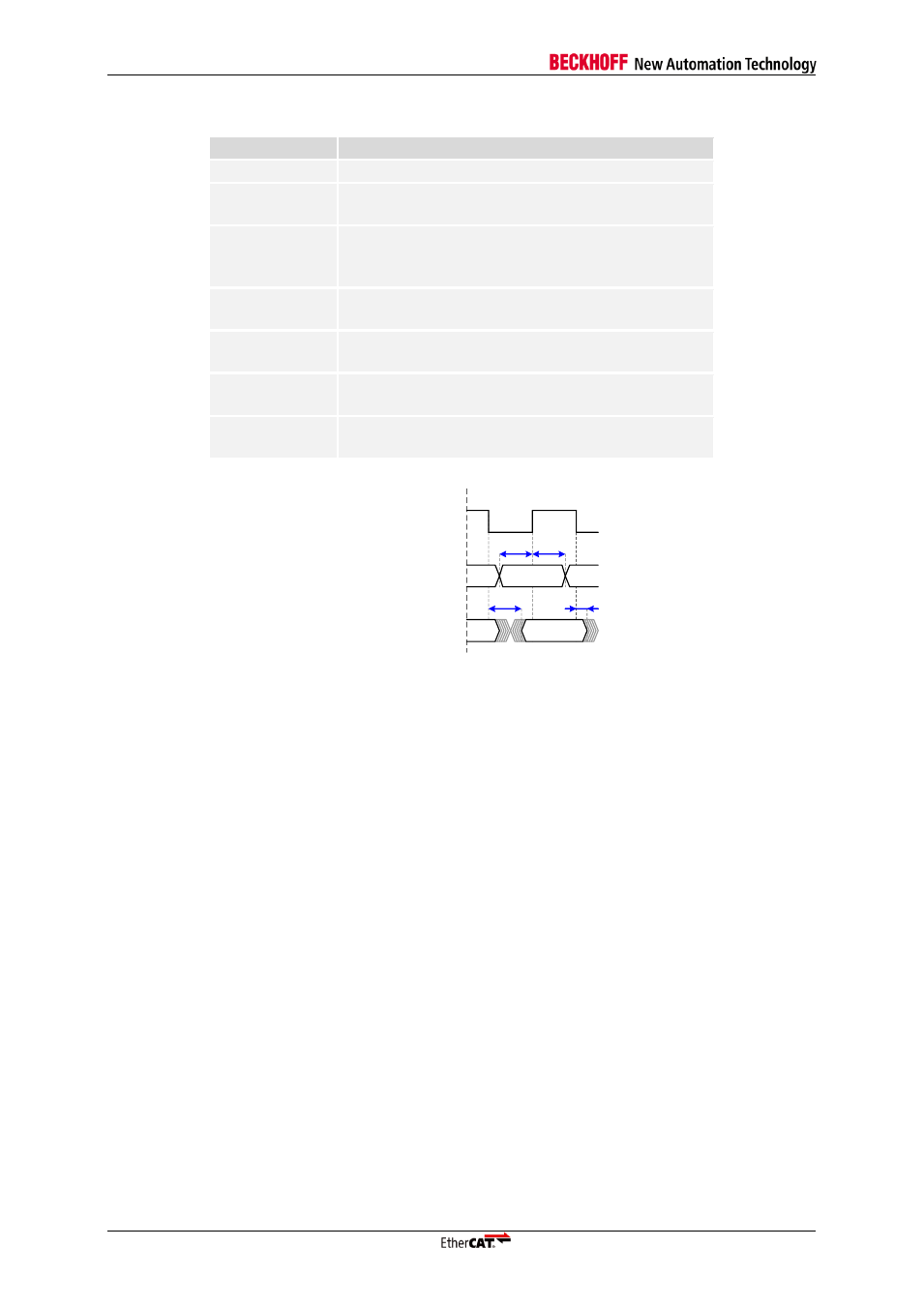

SPI_DO (MISO)

SPI_DI (MOSI)

SPI_CLK*

t

DI_setup

t

DI_hold

t

CLK_to_DO_valid

A

12

t

CLK_to_DO_invalid

I0

7

Figure 45: Basic SPI_DI/SPI_DO timing (*refer to timing diagram for relevant edges of SPI_CLK)

- Bus Terminal System (19 pages)

- EP-xxxx-xxxx (19 pages)

- BK2000 (30 pages)

- LC3100 (67 pages)

- BK4000 (28 pages)

- BK3xx0 (95 pages)

- BK5000 (12 pages)

- LC5200 (32 pages)

- BK7000 (29 pages)

- BK7500 (32 pages)

- BK7300 (40 pages)

- BK8100 (26 pages)

- BC2000 (28 pages)

- BC3100 (51 pages)

- BC7300 (48 pages)

- BC8100 (36 pages)

- BC3150 (112 pages)

- KL1012 (2 pages)

- KL1114 (2 pages)

- KL1164 (1 page)

- KL1232-xxxx (4 pages)

- KL1501 (19 pages)

- KL1512 (15 pages)

- KL2521-0024 (18 pages)

- KL2512 (21 pages)

- KL2612 (4 pages)

- KL2622 (9 pages)

- KL3062 (24 pages)

- KL3064 (20 pages)

- KL4132 (19 pages)

- KL4034 (25 pages)

- KL3302 (23 pages)

- KL3351 (18 pages)

- KS3681 (43 pages)

- KL4112 (18 pages)

- KL5001 (16 pages)

- KL5051 (17 pages)

- KL5101-0012 (21 pages)

- KS5111-0000 (21 pages)

- KL5121 (19 pages)

- KL6021 (20 pages)

- KL6051 (17 pages)

- Z1000 (2 pages)

- KL6071 (12 pages)

- Z1003 (2 pages)