5 physical layer interface, Physical layer interface, Table 22: physical layer general – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 75

IP Core Signals

Slave Controller

– IP Core for Xilinx FPGAs

III-63

8.5

Physical Layer Interface

The IP Core is connected with Ethernet PHYs using MII/RMII/RGMII interfaces.

Table 22 lists the general PHY interface signals.

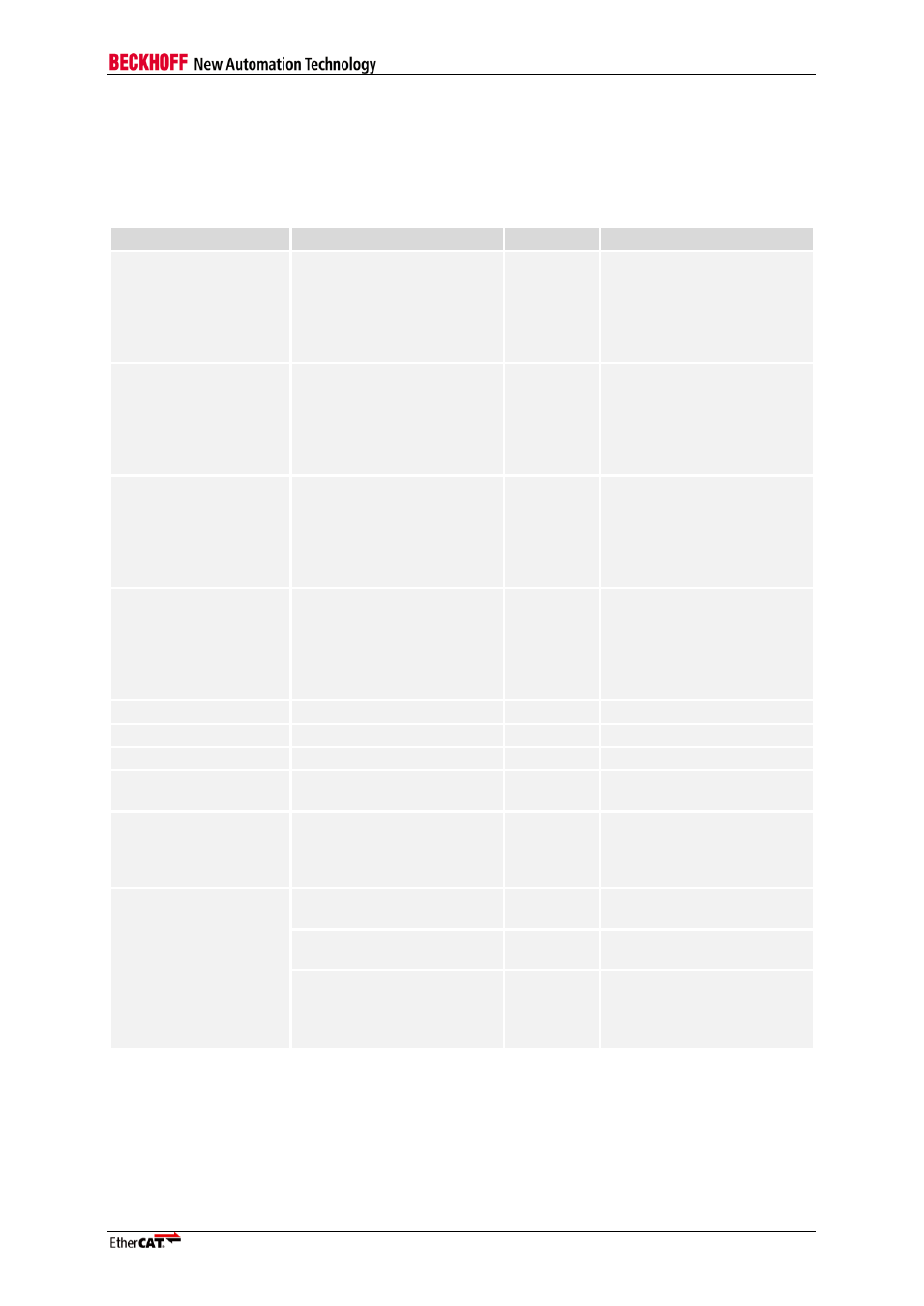

Table 22: Physical Layer General

Condition

Name

Direction

Description

PHY Management

Interface enabled and

Export PHY address as

signals and

not(Independent PHY

addresses)

PHY_OFFSET_VEC[4:0]

INPUT

PHY address offset

PHY Management

Interface enabled and

Export PHY address as

signals and

Independent PHY

addresses

PHY_ADR_PORT0[4:0]

INPUT

PHY address port 0

PHY Management

Interface enabled and

Export PHY address as

signals and

Independent PHY

addresses and Port1

PHY_ADR_PORT1[4:0]

INPUT

PHY address port 1

PHY Management

Interface enabled and

Export PHY address as

signals and

Independent PHY

addresses and Port2

PHY_ADR_PORT2[4:0]

INPUT

PHY address port 2

Port0 enabled

nPHY_RESET_OUT0

OUTPUT

PHY reset port 0 (act. low)

Port1 enabled

nPHY_RESET_OUT1

OUTPUT

PHY reset port 1 (act. low)

Port2 enabled

nPHY_RESET_OUT2

OUTPUT

PHY reset port 2 (act. low)

PHY Management

Interface enabled

MCLK

OUTPUT

PHY management clock

PHY Management

Interface enabled,

Tristate drivers inside

core (EEPROM/MII)

MDIO

BIDIR

PHY management data

PHY Management

Interface enabled,

External tristate drivers

for EEPROM/MI

MDIO_DATA_IN

INPUT

PHY management data:

PHY IP Core

MDIO_DATA_OUT

OUTPUT

PHY management data:

IP Core PHY

MDIO_DATA_ENA

OUTPUT

0: disable output driver for

MDIO_DATA_OUT

1: enable output driver for

MDIO_DATA_OUT

NOTE: MDIO must have a pull-up resistor (4.7k

Ω recommended for ESCs).