5 axi4/axi4 lite on-chip bus, 1 interface, Axi4/axi4 lite on-chip bus – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 133: Interface, Table 61: axi4 lite signals, Figure 60: axi4 signals

PDI Description

Slave Controller

– IP Core for Xilinx FPGAs

III-121

10.5 AXI4/AXI4 LITE On-Chip Bus

10.5.1 Interface

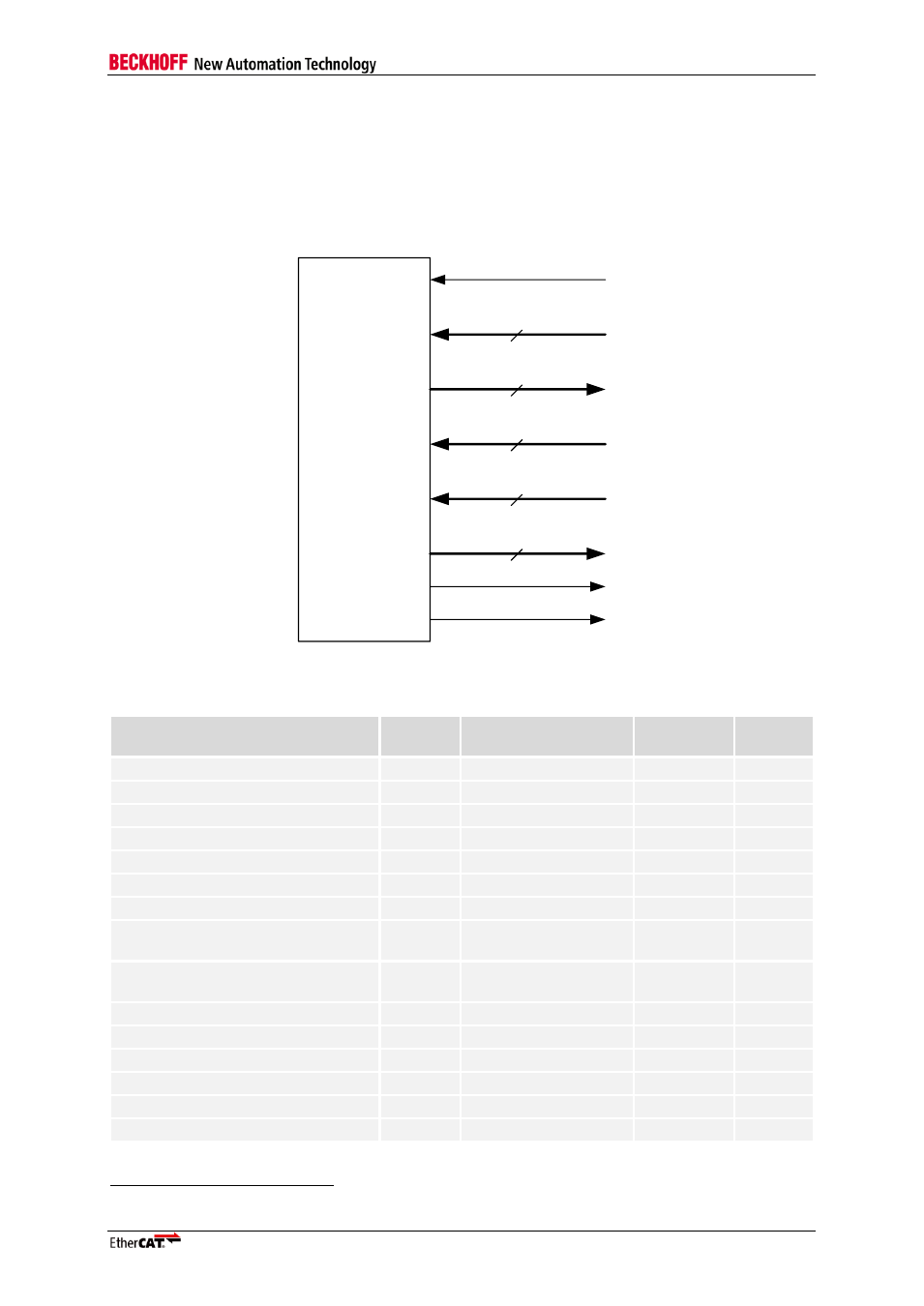

The AXI4 Slave PDI is selected during the IP Core configuration. The signals of the AXI4 interface

are

14

:

EtherCAT

IP core

CLK_PDI_EXT

Read address

channel

Read data

channel

Write address

channel

Write data

channel

Write response

channel

IRQ_MAIN

IRQ_DC_SYNC0/1

Figure 60: AXI4 signals

Table 61: AXI4 LITE signals

Signal

Directio

n

Description

Channel

Signal

polarity

PDI_AXI_ACLK

INPUT

AXI bus clock

PDI_AXI_AWADDR[15:0]

INPUT

Write address

WR addr.

PDI_AXI_AWPROT[2:0]

INPUT

Write protection type

WR addr.

PDI_AXI_AWREGION[3:0]

INPUT

Write region identifier

WR addr.

PDI_AXI_AWQOS[3:0]

INPUT

Write QoS identifier

WR addr.

PDI_AXI_AWVALID

INPUT

Write address valid

WR addr.

act. high

PDI_AXI_AWREADY

OUTPUT Write address ready

WR addr.

act. high

PDI_AXI_WDATA

[PDI_EXT_BUS_WIDTH-1:0]

INPUT

Write data

WR data

PDI_AXI_WSTRB

[PDI_EXT_BUS_WIDTH/8-1:0]

INPUT

Write data byte enable WR data

PDI_AXI_WVALID

INPUT

Write data valid

WR data

act. high

PDI_AXI_WREADY

OUTPUT Write data ready

WR data

act. high

PDI_AXI_BRESP[1:0]

OUTPUT Write response

WR resp.

PDI_AXI_BVALID

OUTPUT Write response valid

WR resp.

act. high

PDI_AXI_BREADY

INPUT

Write response ready

WR resp.

act. high

PDI_AXI_ARADDR[15:0]

INPUT

Read address

RD addr.

14

The prefix `PDI_AXI_` or is added to the AXI interface signals for the IP Core interface.