1 configuration and resource consumption, 2 functionality, Configuration and resource consumption – BECKHOFF EtherCAT IP Core for Xilinx FPGAs v3.00k User Manual

Page 66: Functionality

Example Designs

III-54

Slave Controller

– IP Core for Xilinx FPGAs

6.3

Xilinx Zynq ZC702 Development Kit with AXI (Vivado based)

6.3.1

Configuration and resource consumption

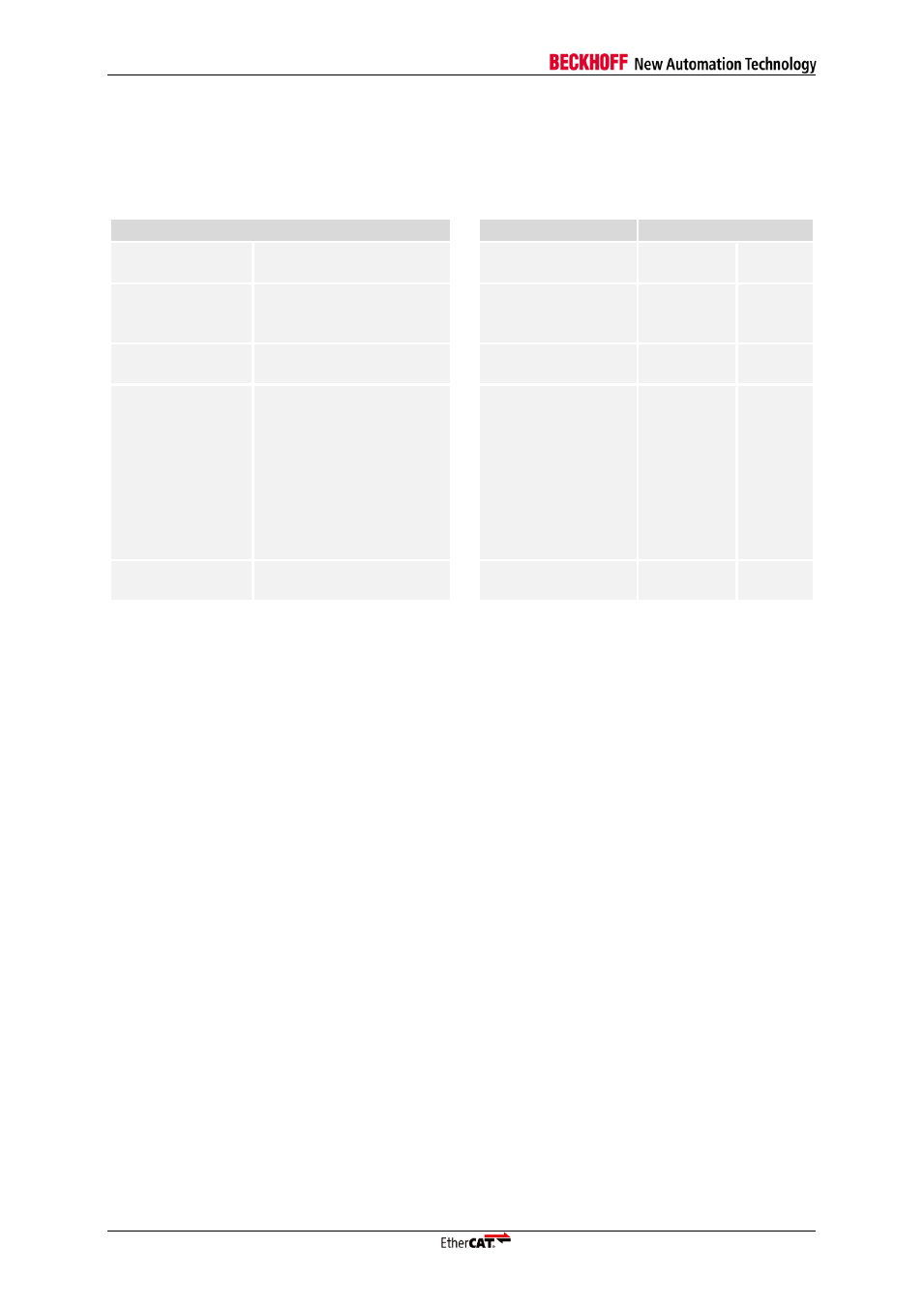

Table 15: Resource consumption Xilinx Zynq ZC702 example design

Configuration

Resources

XZ7Z020

Physical layer

2x MII,

TX Shift, MIIM

Slice Registers

13,467

13 %

Internal Function

4x FMMU

4x SyncManager

1 KB RAM

Slice LUTs

16,360

31 %

Distributed clocks

32 bit,

2x Sync, 2x Latch

Occupied Slices

5,651

42 %

Feature details

AL Status Code register,

Extended Watchdog,

Watchdog counter,

AL Event Mask reg.

EPU and PDI Error

Counter,

Lost link counter,

RUN_LED,

LED Test

Block RAM

RAMB18E1

RAMB36E1

2

1

1 %

1 %

PDI

AXI4 LITE slave, 32 bit,

asynchronous

MMCME2_ADV

1

25 %

NOTE: These resource consumption figures are based on EtherCAT IP Core for Xilinx FPGAs Version 3.00j and

Vivado 2014.2 with AR61518 and the appropriate settings for this answer record.

6.3.2

Functionality

Attach the FMC ISMNET module to FMC1 connector of ZC702 base board. Populate jumper JP6 pins

1-2 (CARRIER_25MHz to CARRIER_25MHZ_S) on ISMNET, because the 25 MHz clock source for

the Ethernet PHYs is also used as the clock source for the EtherCAT IP core in the Zynq FPGA. You

can optionally connect the UART of the ZC702 (J17) to your PC (9600 baud, 8 bit data, 1 stop bit, no

parity, no hardware handshake). The LEDs D3 and D4 on the FMC ISMNET module are used as

Link/Activity LEDs for the two Ethernet ports. Push button SW2 on the ZC702 is used as system reset

input.

The EtherCAT IP Core and the ISMNET PHY ports are only powered and running if the processor

system is running.

The ARM demo application performs the following tasks:

Accept any EtherCAT Slave State request (copying AL Control to AL Status register). Print state

changes via UART.

Copy output data from EtherCAT IP Core (0x1024) to GPIO for LEDs DS15-DS22 on the ZC702.

Print output data from the EtherCAT IP Core (0x1020-0x1023) via UART.

Copy input data from GPIO for push buttons SW5/SW7 on the ZC702 to the EtherCAT IP Core

(0x1000).

Copy input data from GPIO for push buttons SW1-SW2 on the ISMNET module to the EtherCAT

IP Core (0x1002).

Copy input data from GPIO for DIP switches SW12 on the ZC702 to the EtherCAT IP Core

(0x1001).

Copy input data from GPIO for DIP switches SW3 on the ISMNET module to the EtherCAT IP

Core (0x1003).

Copy input data from GPIO for DIGILENT U15 on the ISMNET module to the EtherCAT IP Core

(0x1004).